### **GENERAL DESCRIPTION**

PJ10515/F is high efficiency, synchronous Buck converter with integrated MOSFETs. It operates with 1.5MHz switching frequency and the input supply voltage range of 2.5V to 5.5V, and supports up to 1.5A continuous output current. The duty cycle is up to 100% for the lowest dropout.

At light load, PJ10515 operates in PFM to maintain high efficiency, and PJ10515F operates in FPWM to maintain tight output voltage ripples.

PJ10515/F integrates complete protection features including input under-voltage lock-out (UVLO), input over-voltage protection (OVP), cycle-by-cycle over current limit (OCL), output under-voltage protection with hiccup (UVP), output over-voltage protection (OVP) and over-temperature protection (OTP) to confirm its safe and stable operation at different conditions.

PJ10515/F is available in SOT23-5 package and the junction temperature is specified from -40°C to 125°C.

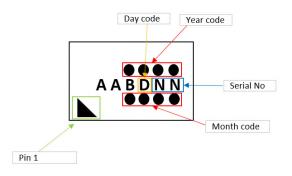

### **MARKING INFORMATION**

### **FEATURES**

- 2.5V to 5.5V Input Voltage Range

- 1.5A Continuous Output Current

- 1.5MHz CCM Switching Frequency

- Support Maximum Duty Cycle : 100%

- ♦ Low Quiescent Current: 45µA

- Low Shutdown Current: 0.1μA

- Peak Current Mode (PCM) Control

- Optional Operation Modes Condition :

- PJ10515 : Pulse Frequency Modulation (PFM)

- PJ10515F : Forced Pulse Width Modulation (FPWM)

- High Reference Voltage Accuracy : 0.6V ±1.0%

- Complete Protections Integrated for Reliability:

- Internal 0.5ms Soft-Start Avoiding Inrush Current

- Cycle-by-Cycle Over Current Limit (OCL) :

Peak Current Limit and Valley Current Limit

- Unlatched VIN UVLO, VIN OVP, UVP, OVP and OTP Protection

- Small Solution Size:

- Small MLCC Output Capacitors Supported

- No External Compensation Needed

- SOT23-5 Package

## **APPLICATIONS**

- Digital Set-Top Box and Surveillance

- TV / Monitor and EPOS

- Home Networking Device and Wireless Router

- Smart Speaker

- 5V/3.3V Distributed Power Systems

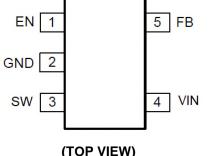

## **PIN CONFIGURATION**

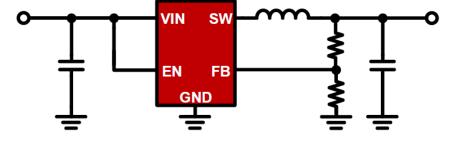

### SIMPLIFIED SCHEMATIC

(TOP VIEW)

## **ORDERING INFORMATION**

| ORDER NUMBER  | Operation<br>Mode | Marking ID | Package | Description                        |

|---------------|-------------------|------------|---------|------------------------------------|

| PJ10515S5_R1  | PFM               | A1BDNN     | SOT23-5 | Halogen Free in T&R, 3000 pcs/Reel |

| PJ10515FS5_R1 | FPWM              | AEBDNN     | SOT23-5 | Halogen Free in T&R, 3000 pcs/Reel |

# **FUNCTIONAL PIN DESCRIPTION**

| TERM   | MINAL | <b>I/O</b> <sup>(1)</sup> | DESCRIPTION                                                                                                                    |  |

|--------|-------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| NUMBER | NAME  |                           |                                                                                                                                |  |

| 1      | EN    | I                         | <b>Enable Control Pin</b> . Drive EN pin high to enable the device or low to disable the device. Do not leave EN pin floating. |  |

| 2      | GND   | G                         | Power Ground and Signal Ground.                                                                                                |  |

| 3      | SW    | Р                         | Switch Node. Connect to power inductor with short and wide trace.                                                              |  |

| 4      | VIN   | Р                         | <b>Input Power Supply.</b> Add a 100nF ceramic decoupling capacitor as close to VIN and GND pins as possible.                  |  |

| 5      | FB    | I                         | <b>Feedback Input</b> . Sense output voltage through the resistor divider for setting and controlling the output voltage.      |  |

(1) I - Input; O - Output; P - Power; G - Ground

## **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                           | PARAMETER                            |      |                      | Unit |

|-------------------------------------------|--------------------------------------|------|----------------------|------|

| Voltage range at terminals <sup>(2)</sup> | VIN, EN                              | -0.3 | 6                    | V    |

|                                           | SW, DC                               | -0.3 | V <sub>IN</sub> +0.3 | V    |

|                                           | SW, Transient <10 ns                 | -3   | 9                    | V    |

|                                           | FB                                   | -0.3 | 5.5                  | V    |

| T <sub>J</sub> <sup>(2)</sup>             | Operating junction temperature range | -40  | 150                  | °C   |

| TSTG                                      | Storage temperature range            | -65  | 150                  | °C   |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Operating at junction temperatures greater than 125°C, although possible, degrades the lifetime of the device.

## HANDLING RATINGS

| PARAMETER          | DEFINITION                                                              | MIN  | МАХ | UNIT |

|--------------------|-------------------------------------------------------------------------|------|-----|------|

|                    | Human Body Model (HBM) ESD stress voltage <sup>(2)</sup>                | -2   | 2   | kV   |

| ESD <sup>(1)</sup> | Charged Device Model (CDM) ESD stress voltage <sup>(3)</sup> , all pins | -500 | 500 | V    |

(1) Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

(2) Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(3) Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **RECOMMENDED OPERATING CONDITIONS**

|                 | PARAMETER                      |     |      | МАХ | UNIT |

|-----------------|--------------------------------|-----|------|-----|------|

| V <sub>IN</sub> | Input voltage range            | 2.5 |      | 5.5 | V    |

| Vout            | Output voltage range           | 0.6 |      | Vin | V    |

| Fsw             | Buck switching frequency range |     | 1500 |     | kHz  |

| Ιουτ            | Output DC current range        | 0   |      | 1.5 | А    |

| TJ              | Operating junction temperature | -40 |      | 125 | °C   |

### **THERMAL INFORMATION**

|                       | THERMAL RESISTANCE                                    | SOT23-5 | UNIT |

|-----------------------|-------------------------------------------------------|---------|------|

| $\Theta_{JA}{}^{(1)}$ | Junction to ambient thermal resistance (Specific EVM) | 65      | °C/W |

(1) R<sub>BJA(EVM)</sub> is based on the thermal resistance information measured during the actual operation of the corresponding evaluation Module. EVM information: 60mm x 45mm, FR-4, TG150, 1.6mm thickness, 2-layer 2-Oz Cu copper. Operating Condition: V<sub>IN</sub> = 5V, V<sub>OUT</sub> = 1.8V, I<sub>OUT</sub> = 1.5A, T<sub>A</sub> = 25°C. This thermal resistance information is for reference only. The actual thermal resistance depends on PCB board layout, and test environment conditions.

## **ELECTRICAL CHARACTERISTICS**

$T_J$  = -40°C to 150°C,  $V_{IN}$  = 5V. Typical value is tested at  $T_J$  = +25°C, unless otherwise noted.

|                                         | PARAMETER                             | TEST CONDITIONS                                         | MIN   | ТҮР   | MAX   | UNIT |

|-----------------------------------------|---------------------------------------|---------------------------------------------------------|-------|-------|-------|------|

| SUPPLY V                                | OLTAGE                                |                                                         |       |       |       |      |

| V <sub>IN</sub>                         | Input voltage range                   |                                                         | 2.5   |       | 5.5   | V    |

|                                         |                                       | V <sub>IN</sub> rising                                  | 2.3   | 2.4   | 2.5   | V    |

| $V_{\text{IN}\_\text{UVLO}}$            | Under voltage lockout threshold       | V <sub>IN</sub> falling                                 | 2.1   | 2.2   | 2.3   | V    |

|                                         |                                       | V <sub>IN</sub> Hysteresis                              |       | 0.2   |       | V    |

|                                         | Quiescent current into the VIN        | Non-switching, $V_{EN} = 5 V$ ,                         |       | 45    |       | μA   |

| lq                                      | pin, PJ10515                          | $V_{FB} = V_{REF}^* 105\%, I_{OUT} = 0 \text{ A}$       |       | 40    |       | μΛ   |

| īQ                                      | Quiescent current into the VIN        | Non-switching, $V_{EN} = 5 V$ ,                         |       | 50    |       | μA   |

|                                         | pin, PJ10515F                         | $V_{FB} = V_{REF}^{*}105\%, I_{OUT} = 0 \text{ A}$      |       | 00    |       | μΛ   |

| I <sub>SD</sub>                         | Shutdown current into the VIN pin     | IC disabled, $V_{\text{IN}}$ = 5V, $V_{\text{EN}}$ = 0V |       | 0.1   |       | μA   |

| EN                                      |                                       |                                                         |       |       |       |      |

| $V_{\text{EN}\_\text{H}\_\text{R}}$     | EN input level to start switching     | Rising threshold                                        |       | 0.88  | 1.15  | V    |

| $V_{\text{EN}_{-}\text{H}_{-}\text{F}}$ | EN input level to stop switching      | Falling threshold                                       | 0.5   | 0.75  |       | V    |

| FB                                      |                                       |                                                         |       |       |       |      |

|                                         |                                       | T <sub>J</sub> = 25 ℃                                   | 0.594 | 0.6   | 0.606 | V    |

| $V_{FB}$                                | FB Voltage                            | $T_J = -40$ °C to 125 °C                                | 0.591 | 0.6   | 0.609 | V    |

| $I_{FB(LKG)}$                           | FB Input Leakage Current              | T <sub>J</sub> = 25 °C                                  | -100  | 0     | 100   | nA   |

| STARUP                                  |                                       | I                                                       |       |       |       |      |

| T <sub>ss</sub>                         | Internal Fixed Soft-start Time        | 10% V <sub>OUT</sub> to 90% V <sub>OUT</sub>            |       | 0.5   |       | mS   |

| T <sub>DLY</sub>                        | EN Delay Time                         | EN High to 1 <sup>st</sup> Switching Pulse              |       | 240   |       | uS   |

| SWITCHIN                                | IG FREQUENCY                          | 1                                                       | 1     |       |       | 1    |

| F <sub>sw</sub>                         | Switching Frequency, CCM<br>Operation | VIN = 5V, VOUT = 1.8V, CCM                              |       | 1,500 |       | kHz  |

| POWER ST                                | AGE                                          |                                        |      |       |      |    |

|-----------------------------------------|----------------------------------------------|----------------------------------------|------|-------|------|----|

| R <sub>DSON(HS)</sub>                   | High-Side MOSFET<br>On-Resistance            | $T_{\rm J} = 25$ °C, $V_{\rm IN} = 5V$ |      | 200   |      | mΩ |

| R <sub>DSON(LS)</sub>                   | Low-Side MOSFET<br>On-Resistance             | $T_J = 25 \ ^\circ C, \ V_{IN} = 5V$   |      | 135   |      | mΩ |

| T <sub>ON_MIN</sub> <sup>(1)</sup>      | Minimum On Pulse Width                       |                                        |      | 80    |      | nS |

| T <sub>DEAD</sub>                       | Dead Time                                    |                                        |      | 10    |      | nS |

| OVER CUR                                | RENT PROTECTION                              | 1                                      |      |       |      |    |

| I <sub>LS(OC)</sub>                     | Low-side Valley Current Limit                | V <sub>IN</sub> = 5V                   |      | 1.8   |      | А  |

| I <sub>HS(OC)</sub>                     | High-side Valley Current Limit               | V <sub>IN</sub> = 5V                   |      | 2.5   |      | Α  |

| I <sub>LS(NOC)</sub>                    | Low-side Negative Current Limit,<br>PJ10515F | V <sub>IN</sub> = 5V <sup>°</sup>      |      | 0.8   |      | А  |

| OUTPUT OV                               | /P AND UVP                                   |                                        |      |       |      |    |

| $V_{\text{IN}\_\text{OVP}\_\text{R}}$   | V <sub>IN</sub> OVP Rising Threshold         |                                        | 5.95 | 6.05  | 6.15 | V  |

| $V_{\text{IN\_OVP}\_\text{F}}$          | V <sub>IN</sub> OVP Failing Threshold        |                                        | 5.6  | 5.7   | 5.8  | V  |

| $V_{\text{IN}\_\text{OVP}\_\text{HYS}}$ | V <sub>IN</sub> OVP Hysteresis               |                                        |      | 0.35  |      | V  |

| $V_{\text{OUT\_OVP\_R}}$                | Output OVP Rising                            |                                        |      | 116%  |      |    |

| $V_{\text{OUT\_OVP}\_\text{F}}$         | Output OVP Falling                           |                                        |      | 111%  |      |    |

| $V_{\text{OUT}\_\text{UVP}\_\text{F}}$  | Output UVP Failing                           |                                        |      | 66.7% |      |    |

| $V_{\text{OUT}\_\text{UVP}\_\text{R}}$  | Output UVP Rising                            |                                        |      | 73%   |      |    |

| T <sub>HCP(WAIT)</sub>                  | Wait Time before Entering UV<br>Hiccup       |                                        |      | 90    |      | uS |

| $T_{\text{HCP}(\text{OFF})}$            | UVP Hiccup Time before<br>Re-startup         |                                        |      | 4.5   |      | mS |

| OVER TEMP                               | PERATURE PROTECTION                          |                                        | •    |       |      |    |

| т                                       | Thermal shutdown temperature                 |                                        |      | 150   |      | °C |

| T <sub>SD</sub>                         | Thermal shutdown hysteresis                  |                                        |      | 30    |      | °C |

(1) Guaranteed by design

## **FEATURE DESCRIPTION**

#### Overview

PJ10515/F operates at input supply voltage range of 2.5V to 5.5V, and supports up to 1.5A continuous output current. PJ10515/F operates with 1.5MHz switching frequency. The buck converter integrates high-side and low-side MOSFETs (HS-FET and LS-FET), adopts peak current mode (PCM) control to provide fast transient response without external loop compensation, which can help to save output capacitors and reduce solution size.

#### **Device Operation Modes**

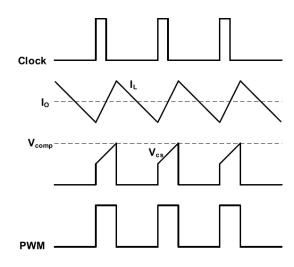

#### **Continuous Current Mode (CCM)**

When the load current is higher than half of the peak inductor current, the converter operates in CCM. In CCM, the switching frequency is fixed and the output voltage ripple is the smallest. The device can provide a maximum continuous output current of 1.5A.

As shown in Figure-1, during CCM operation, the internal clock initiates one pulse, and the HS-FET is turned on, with the inductor current ramping up. When the inductor current reaches the COMP voltage, the HS-FET is turned off and the LS-FET is turned on, with the inductor current decreasing until the next rising edge of the clock. The switching frequency depends on the internal clock and is therefore fixed.

Figure-1 PCM control schema waveform

#### **Pulse Frequency Modulation (PFM)**

PJ10515 automatically enters PFM at light-load condition to maintain high efficiency. As the load current decreases, the inductor current reduces as well and eventually comes to a point that its ripple valley reaches zero level, which is the boundary between CCM and DCM. The LS-FET is turned off when the inductor crossing zero is detected. As the load current further decreases, the converter runs into DCM.

As the load current is lowered, the required peak current on each switching cycle is lessened and the COMP voltage is reduced by the error amplifier. When the COMP voltage is clamped, the switching frequency will decrease to maintain high efficiency operation.

#### Forced Pulse Width Modulation (FPWM)

PJ10515F operates in FPWM at light-load condition to maintain constant switching frequency and tight output voltage ripples. The LS-FET is forced on when the HS-FET is in its off state and after the dead time, until the next cycle HS-FET is turned on. This mode allows inductor current flowing from output capacitor to the switching node through LS-FET's drain-to-source terminals, which is called negative current. In this case, the switching frequency nearly keeps constant over full range of load current achieving tight output voltage ripples.

#### **Precise Enable Control**

PJ10515/F provides an EN pin, as an external IC enable control, to enable or disable the device. When the EN pin voltage rises above the rising threshold voltage ( $V_{EN(R)}$ ) while the VIN voltage is higher than VIN under-voltage lock-out threshold ( $V_{UVLO(R)}$ ), the device turns on. If the EN pin voltage is pulled below the falling threshold voltage ( $V_{EN(F)}$ ), the regulator stops switching and enters the shutdown mode, that is, the regulator is disabled, and switching is inhibited even if the VIN voltage is above VIN under-voltage lock-out threshold ( $V_{UVLO(R)}$ ). Do not leave the EN pin floating.

#### Soft Start and Pre-biased Soft Start

PJ10515/F provides an internal soft-start feature to ensure inrush control and smooth output voltage ramping during power-up, and the output voltage starts to rise after a 240 $\mu$ s delay from EN rising edge. When the IC starts, the soft-start circuitry generates a soft-start voltage (SS) ramping up from 0V. When it is below the internal reference voltage (V<sub>REF</sub>), SS overrides V<sub>REF</sub> so the error amplifier and comparator use SS as the reference voltage. The output voltage smoothly ramps up. Once SS rises above V<sub>REF</sub>, VREF regains control. At this time the soft start process ends, and PJ10515/F enters steady state operation. The soft start time (T<sub>SS</sub>) is internal fixed at around 0.5ms (10%V<sub>OUT</sub> to 90%V<sub>OUT</sub>).

If the output capacitor is pre-biased at startup, the PJ10515/F initiates switching and start ramping up only after the internal reference voltage becomes greater than the feedback voltage  $V_{FB}$ . This scheme ensures that the converters ramp up smoothly into regulation point.

#### Output UVP with Hiccup mode

PJ10515/F integrates output under-voltage protection (UVP) against over-load or short-circuited condition by constantly monitoring the feedback voltage V<sub>FB</sub>. If V<sub>FB</sub> drops below the under-voltage protection trip threshold (V<sub>UVP</sub>), the UV comparator will go high to turn off both the internal HS-FET and LS-FET.

If the output under-voltage condition continues for a period time of  $T_{HCP(WAIT)}$ , PJ10515/F will enter output UVP with hiccup mode. During hiccup mode, the IC will shut down for a period time of T<sub>HICCUP(OFF)</sub>, and then attempt to recover automatically. Upon completion of the soft-start sequence, if the fault condition is removed, the converter will resume normal operation; otherwise, such cycle for auto-recovery will be repeated until the fault condition is cleared. The hiccup mode allows the circuit to operate safely with low input current and power dissipation, and then the converter resumes normal operation as soon as the over-load or short-circuit condition is removed.

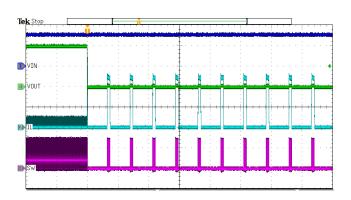

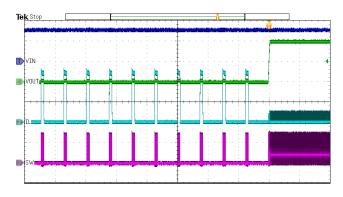

Figure-2. UVP Hiccup mode

#### Peak and Valley Over-Current Limit

PJ10515/F has cycle-by-cycle peak over current limit control (OCL). During HS-FET on state, when the sensed inductor current reaches the current reference generated by the COMP voltage, HS-FET will turn off. When the over-current condition happens and the output voltage drops, the COMP voltage will bet set high. The COMP voltage has a maximum clamp internally, generating the peak current limit (I<sub>HS(OC)</sub>), which limit the output current.

PJ10515/F also has cycle-by-cycle valley over current limit control (OCL). The inductor current is monitored during the LS-FET on state. At the end of a clock cycle, if the sensed inductor current is higher than the valley current limit ( $I_{LS(OC)}$ ), the HS-FET will not turn on, and the LS-FET will keep on state. At the next clock cycle, if the sensed inductor current is lower than  $I_{LS(OC)}$ , the HS-FET will turn on.

If the output load current exceeds the available inductor current (limited between  $I_{HS(OC)}$  and  $I_{LS(OC)}$ ), the output capacitor needs to supply the extra current so that the output voltage will begin to drop. If it drops below the output under-voltage protection threshold (V<sub>UVP</sub>), the IC will stop switching into UV hiccup mode to avoid excessive heat.

### Negative Over-Current Limit (PJ10515F only)

PJ10515F is the part which is FPWM part and allows negative current operation. In case of FPWM operation, high negative current may be generated as an external power source is tied to output terminal unexpectedly. As the risk described above, the internal circuit monitors negative current in each on-time interval of low-side MOSFET and compares it with negative over-current limit threshold (I<sub>NOC</sub>). Once the negative current exceeds the NOC threshold, the low-side MOSFET will be turned off immediately, and then the high-side MOSFET will be turned off to the output inductor. This behavior can keep the valley of negative current at NOC threshold to protect LS-FET.

### **Output Over-Voltage Protection**

PJ10515/F integrates output over-voltage protection (OVP) to minimize output voltage overshoot and protect down-stream devices when recovering from output fault conditions or strong unload transients. The OVP circuitry detects overvoltage condition by monitoring the feedback voltage (V<sub>FB</sub>). When V<sub>FB</sub> rises above the OVP threshold (V<sub>OVP</sub>), the OVP comparator output turns high and both HS-FET and LS-FET are turned off to avoid V<sub>OUT</sub> further rising higher. Once the V<sub>OUT</sub> drops below V<sub>OVP</sub> falling threshold, the IC starts switching again. This function is a non-latch operation.

### Input Over-Voltage Protection

PJ10515/F integrates input over voltage protection (OVP). The OVP circuitry detects over-voltage condition by monitoring the input voltage (V<sub>IN</sub>). When V<sub>IN</sub> rises above the OVP threshold (V<sub>IN(OVP)</sub>), the OVP comparator output turns high and both HS-FET and LS-FET are turned off, the device stops working.

Once  $V_{IN}$  drops below  $V_{IN(OVP)}$  falling threshold, the IC starts switching again. This function can ensure the reliability when the input voltage is unstable with overvoltage spike.

### **Over Temperature Protection**

PJ10515/F includes an over-temperature protection (OTP) circuitry to prevent overheating due to excessive power dissipation. The OTP will shut down switching operation when junction temperature exceeds a thermal shutdown threshold ( $T_{J(SD)}$ ). Once the junction temperature cools down by a thermal shutdown hysteresis ( $T_{J(HYS)}$ ), the IC will resume normal operation with a complete soft start.

## **APPLICATION INFORMATION**

#### Overview

The output stage of synchronous buck converter is mainly composed of inductor and capacitors. By switching the internally integrated power MOSFET, the energy is stored and transferred to the load, and the second-order LC filter is formed to smooth the switching node voltage so that the stable output DC voltage is obtained. This section describes the detailed design process based on one design example.

#### **Output Voltage Setting**

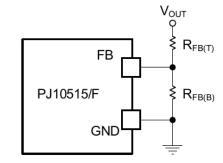

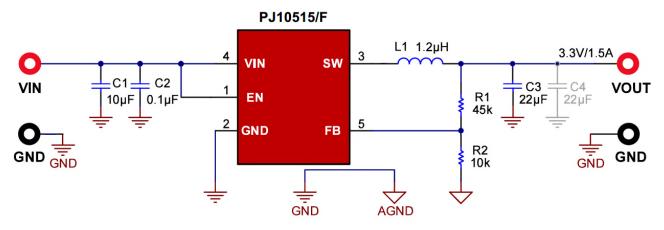

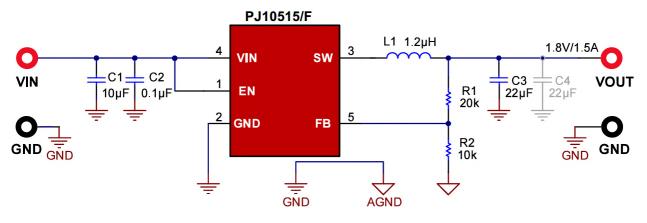

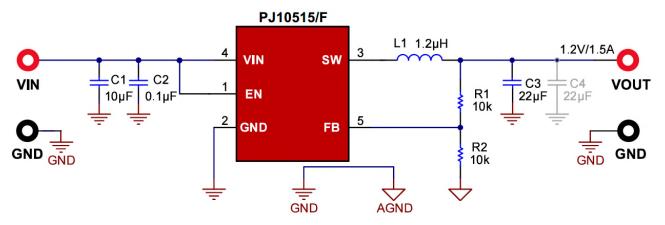

As shown in Figure-4, PJ10515/F can be set to different output voltages by using an external voltage resistor divider connected to the FB pin.

$$V_{_{OUT}} = V_{_{REF}} \times \left(1 + \frac{R_{_{FB(T)}}}{R_{_{FB(B)}}}\right)$$

where  $V_{REF} = 0.6V$

Figure-4. Output voltage setting

It is recommended to design from the bottom side feedback resistor  $R_{FB(B)}$ . Too large  $R_{FB(B)}$  will make the FB pin more susceptible to external noises, while too small  $R_{FB(B)}$  will increase the power loss of the resistor divider.  $R_{FB(B)} = 10k\Omega \sim 50k\Omega$  is recommended. And the top side feedback resistor  $R_{FB(T)}$  can be calculated by the following formula :

$$\mathsf{R}_{\mathsf{fb}(\mathsf{T})} = \mathsf{R}_{\mathsf{fb}(\mathsf{B})} \times \left(\frac{\mathsf{V}_{\mathsf{out}}}{\mathsf{V}_{\mathsf{ref}}} - 1\right)$$

where  $V_{REF} = 0.6V$

For example, in the application with 1.8V output voltage, choose  $R_{FB(B)}$  as  $10k\Omega$  and then  $R_{FB(T)}$  is calculated as  $20k\Omega.$

In the application scenarios where higher precision of output voltage is required, it is recommended to select a voltage resistor divider with a precision of 1% or even higher.

### **Output Inductor Selection**

The selection of inductor is related to the size, cost, efficiency, and transient response performance. Three key parameters of inductor are mainly considered: inductance (L), saturation current (I<sub>SAT</sub>) and inductor DC resistance (DCR).

To compromise the volume and power consumption of the inductor, it is recommended to select an inductor whose current ripple ( $\Delta I_L$ ) is 20%-50% of the rated current (I<sub>rated</sub>) of PJ10515/F, as shown in the following formula :

$$L = \frac{V_{\text{out}} \times \left(V_{\text{IN}} - V_{\text{out}}\right)}{V_{\text{IN}} \times f_{\text{sw}} \times \Delta I_{\text{L}}} = \frac{V_{\text{out}} \times \left(V_{\text{IN}} - V_{\text{out}}\right)}{V_{\text{IN}} \times f_{\text{sw}} \times I_{\text{rated}} \times K_{\text{L}}}$$

where

VIN is input voltage,

Vout is output voltage,

f<sub>SW</sub> is switching frequency,

$I_{\text{rated}}$  is the rated current of PJ10515/F : 1.5A

K∟ is 20%-50%

Once the inductor has been selected according to the above formula, the actual inductor current ripple  $\Delta I_L$

and peak current  $(I_{L(peak)})$  can be obtained by the following formula :

$$\Delta I_{L} = \frac{V_{\text{out}} \times \left(V_{\text{N}} - V_{\text{out}}\right)}{V_{\text{IN}} \times f_{\text{SW}} \times L}$$

$$I_{\text{L(peak)}} = I_{\text{OUT(MAX)}} + \frac{\Delta I_{\text{L}}}{2}$$

where

IOUT(MAX) is maximum output current

The inductor whose saturation current  $I_{SAT}$  is at least greater than the peak current  $I_{L(peak)}$  should be selected with a some margin (for example, 10%) to ensure that the inductor will not be saturated during normal steady-state operation of the chip.

#### **Output Capacitor Selection**

The selection of output capacitor is related to the output voltage ripple, load transient performance and loop stability.

Output voltage ripple  $V_{RIPPLE}$  consists of two main parts. One is the resistive ripple  $V_{RIPPLE(ESR)}$ generated by the inductive current at the equivalent series resistance ESR of the output capacitor. The other part is capacitive ripple  $V_{RIPPLE(C)}$  generated by charging and discharging the output capacitor with the inductance ripple current. The calculation formula is as follows :

$$V_{\text{RIPPLE}} = \sqrt{V_{\text{RIPPLE(ESR)}}^2 + V_{\text{RIPPLE(C)}}^2}$$

$$V_{\text{RIPPLE}(\text{ESR})} = \Delta I_{\text{L}} \times \text{ESR}$$

$$V_{\text{RIPPLE}(\text{C})} = \frac{\Delta I_{\text{L}}}{8 \times C_{\text{out}} \times f_{\text{sw}}}$$

## PJ10515/F 5.5V, 1.5A, 1.5MHz High Efficiency Synchronous, Buck Converter In a SOT23-5 Package

The actual ripple can be simply estimated as :

$$\begin{split} & \mathsf{V}_{\mathsf{RIPPLE}} \; > \; \mathsf{Max} \big( \mathsf{V}_{\mathsf{RIPPLE}(\mathsf{ESR})}, \, \mathsf{V}_{\mathsf{RIPPLE}(\mathsf{C})} \big) \\ & \mathsf{V}_{\mathsf{RIPPLE}} \; < \; \mathsf{V}_{\mathsf{RIPPLE}(\mathsf{ESR})} \; + \; \mathsf{V}_{\mathsf{RIPPLE}(\mathsf{C})} \end{split}$$

### **Input Capacitor Selection**

Since the input current of Buck converter is pulsed discontinuous current, it is recommended to use ceramic capacitors at the input to provide pulsed input current to keep the DC input voltage stable. The input voltage ripple can be calculated by the following formula :

$$V_{IN(Ripple)} \approx D \times I_{OUT} \times \frac{1 - D}{C_N \times f_{sw}} + I_{OUT} \times ESR$$

where

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{IN}}}$$

In addition, since the input capacitor is pulsed discontinuous current, the selected input capacitor must be able to withstand large AC RMS current :

$$I_{_{IN(RMS)}} \approx I_{_{OUT(MAX)}} \times \sqrt{D(1-D)}$$

In addition, to optimize the EMI performance and ensure the reliable and stable operation of the chip, besides using the ceramic capacitor as the input capacitor CIN, it is recommended to add another 0.1µF ceramic capacitor (0603/0402 package) to the VIN and GND pins as close as possible. It is important to note that although the ceramic capacitor has excellent high-frequency performance and stable lifetime, but due to the low ESR characteristics of ceramic capacitor, the actual input voltage may start ringing in some input hot-plug scenarios, and the worst input voltage even may ring to 2 times nominal voltage, thus this over-voltage ringing may breakdown IC. In this case, it is recommended to add an additional electrolytic capacitor with large ESR in parallel at the input voltage end or to add a TVS diode to limit or clamp the input over-voltage ringing.

| V <sub>OUT</sub> (V) | R <sub>FB(T)</sub> (kΩ) | R <sub>FB(B)</sub> (kΩ) | L <sub>typ</sub> (µH) | CIN        | Соит |

|----------------------|-------------------------|-------------------------|-----------------------|------------|------|

| 3.3                  | 45                      | 10                      | 1.2                   | 10µF+100nF | 22µF |

| 2.5                  | 31.7                    | 10                      | 1.2                   | 10µF+100nF | 22µF |

| 1.8                  | 20                      | 10                      | 1.2                   | 10µF+100nF | 22µF |

| 1.2                  | 10                      | 10                      | 1.2                   | 10µF+100nF | 22µF |

| 1.05                 | 7.5                     | 10                      | 1.2                   | 10µF+100nF | 44µF |

The recommended component selection is shown in Table -1.

#### Table-1. Recommended Component Selection Table

### **Feedforward Capacitor Selection**

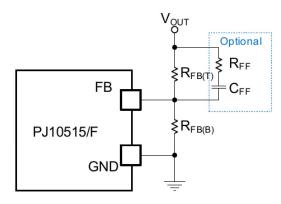

PJ10515/F integrates internal loop compensation, which can simplify the external circuit design and achieve fast load transient response performance. In some applications where the load transient response is more demanding, the transient response performance can be further improved by adding feedforward resistor R<sub>FF</sub> and capacitor C<sub>FF</sub> across the top FB divider resistor. In consideration of noise coupling, it is recommended to use  $R_{FF} = 2k\Omega \sim 10k\Omega$ , and do not use CFF higher than 47pF. Note that the actual RFF and CFF are optional devices, and it is recommended to optimize the selection through bench checks of load transient response and load regulation performance.

#### Figure-5. Feedforward Resistor and Capacitor

#### **PCB Design Guidelines**

PCB design is a critical portion of good power supply design. The following guidelines will help users design a PCB with the best power conversion performance, thermal performance, and minimized generation of unwanted EMI.

- 1. Place the input ceramic capacitor as close to VIN and GND pins as possible.

- The trace of the main power loop CIN→L→COUT→GND should be as short and wide as possible to reduce trace voltage drop and improve conversion efficiency.

- 3. The SW node voltage is high frequency square wave. Appropriately reducing the size of SW node can improve EMI performance; On the other hand, appropriately increasing the size of node SW optimize heat dissipation can performance. Take appropriate compromise according to the actual situation is recommended.

- 4. The FB trace should be as far away from noise sources as possible, such as SW node.

- 5. The sampling point of the output voltage VOUT should be placed near the end of the output capacitors and place the voltage divider resistors near the FB pin.

- 6. The trace and copper of VIN and GND node should be as wide as possible to help heat dissipation. In multilayer PCB designs, it is recommended to leave a complete GND layer for the GND node and to add enough vias between the GND layer and the chip layer. The vias can optimize heat dissipation performance.

## **Typical Reference Design**

Figure-6.  $V_{IN}$ = 5V,  $V_{OUT}$ = 3.3V,  $I_{OUT}$ = 1.5A

Figure-7. V<sub>IN</sub>= 5V, V<sub>OUT</sub>= 1.8V, I<sub>OUT</sub>= 1.5A

Figure-8. VIN= 5V, VOUT= 1.2V, IOUT= 1.5A

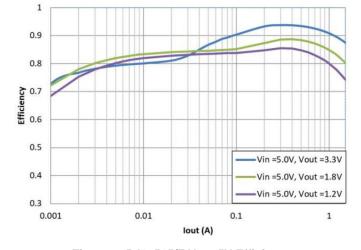

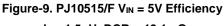

## **Typical Operating Characteristics**

Test Conditions:  $V_{IN} = 5V$ ,  $V_{OUT} = 1.8V$ ,  $T_A = 25^{\circ}C$  (unless otherwise noted)

$L = 1.5 \mu H$ , DCR =  $12.1 m \Omega$

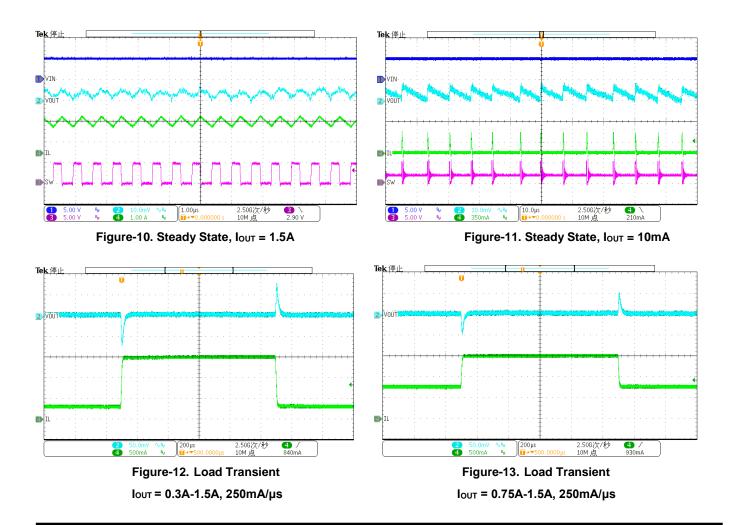

## **PACKAGE DIMENSION**

| Complex | Dimensions | (Millimeters) | Dimensions | s (Inches) |

|---------|------------|---------------|------------|------------|

| Symbol  | Min.       | Max.          | Min.       | Max.       |

| А       | -          | 1.350         | 0.035      | 0.047      |

| A1      | 0.000      | 0.150         | 0.000      | 0.006      |

| A2      | 1.000      | 1.200         | 0.039      | 0.047      |

| b       | 0.300      | 0.500         | 0.012      | 0.020      |

| С       | 0.100      | 0.220         | 0.004      | 0.009      |

| D       | 2.820      | 3.020         | 0.111      | 0.119      |

| E       | 1.500      | 1.700         | 0.059      | 0.067      |

| E1      | 2.600      | 3.000         | 0.102      | 0.118      |

| е       | 0.950      | 0.950 (BSC)   |            | BSC)       |

| e1      | 1.800      | 2.000         | 0.071      | 0.079      |

| L       | 0.300      | 0.600         | 0.012      | 0.024      |

| θ       | 0°         | 8°            | 0°         | 8°         |

# Disclaimer

- Reproducing and modifying information of the document is prohibited without permission from Panjit International Inc..

- Panjit International Inc. reserves the rights to make changes of the content herein the document anytime without notification. Please refer to our website for the latest document.

- Panjit International Inc. disclaims any and all liability arising out of the application or use of any product including damages incidentally and consequentially occurred.

- Panjit International Inc. does not assume any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

- Applications shown on the herein document are examples of standard use and operation. Customers are responsible in comprehending the suitable use in particular applications. Panjit International Inc. makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

- The products shown herein are not designed and authorized for equipments requiring high level of reliability or relating to human life and for any applications concerning life-saving or life-sustaining, such as medical instruments, transportation equipment, aerospace machinery et cetera. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Panjit International Inc. for any damages resulting from such improper use or sale.

- Since Panjit uses lot number as the tracking base, please provide the lot number for tracking when complaining