## PM30003V-0405 Datasheet

Version: 0.5.06

Release Date: 2025-04-30

MetaWells Co., Ltd.

www. MetaWells. com

## **Contents**

| 1 Introduction                   | .1 |

|----------------------------------|----|

| 2 Product Description            | .2 |

| 2.1 Product Features             | .3 |

| 2.2 Device Overview              | .5 |

| 3 Function Introduction          | .6 |

| 3.1 Block Diagram                | .6 |

| 3.2 System Block Diagram         | .6 |

| 3.3 Memory Mapping Configuration | .7 |

| 3.4 Memory                       | .8 |

| 3.4.1 Flash                      | .8 |

| 3.4.2 SRAM                       | .8 |

| 3.5 CRC calculation unit         | .9 |

| 3.6 Power Supply Plan            | .9 |

| 3.7 Power Monitor                | .9 |

| 3.8 Low power consumption mode   | .9 |

| 3.9 Reset                        | .9 |

| 3.9.1 System Reset               | .9 |

| 3.9.2 Power reset                | .0 |

| 3.10 Clock and clock tree1       | .0 |

| 3.11 SYSCFG1                     | .2 |

| 3.12 GPIO1                       | .2 |

| 3.13 Interruptions and Events1   | .2 |

| 3.13.1 NVIC                      | .2 |

| 3.13.2 EXTI                      | .3 |

| 3.14 ADC1                        | .3 |

| 3.15 Timer1                      | .3 |

| 3.15.1 Advanced Timer1           | 4  |

| 3.15.2 General Timer1            | .4 |

| 3.15.3 Basic Timer1              | 4  |

| 3.16 AWUT Timer                                         | 15 |

|---------------------------------------------------------|----|

| 3.17 Independent Watchdog(IWDG)                         | 15 |

| 3.18 Window Watchdog(WWDG)                              | 15 |

| 3.19 System Tick Timer                                  | 15 |

| 3.20 I2C Bus                                            | 15 |

| 3.21 Universal asynchronous receiver transmitter (UART) | 16 |

| 3.22 Serial Peripheral Interface (SPI)                  | 16 |

| 3.23 Operational Amplifier                              |    |

| 3.24 Built-in Driver                                    |    |

| 3.25 Input and Output Truth Table                       | 17 |

| 3.25.1 Straight-through Prevention Function             | 17 |

| 3.25.2 Dead Zone Function                               | 18 |

| 3.26 LDO                                                | 18 |

| 3.27 MOSFET                                             | 19 |

| 3.28 96-bit UID                                         | 19 |

| 3.29 Debugging Interface                                | 19 |

| 4 Electrical Characteristics                            | 20 |

| 4.1 Power Supply                                        | 20 |

| 4.2 Maximum Absolute Ratings                            | 21 |

| 4.2.1 Limit Voltage Characteristics                     | 21 |

| 4.2.2 Extreme Current Characteristics                   | 21 |

| 4.2.3 Limit Temperature Characteristics                 | 22 |

| 4.3 Operating Parameters                                | 22 |

| 4.3.1 Recommended Operating Conditions                  | 22 |

| 4.3.2 On/Off Reset Characteristics                      | 22 |

| 4.3.3 Under-voltage Reset Characteristics               | 23 |

| 4.3.4 Internal Reference Voltage                        | 23 |

| 4.3.5 Operating Current Characteristics                 | 24 |

| 4.3.6 Internal High-speed HSI Clock Characteristics     | 24 |

| 4.3.7 Internal Low-speed LSI Clock Characteristics      | 25 |

| 4.3.8 GPIO External clock input characteristics | 25 |

|-------------------------------------------------|----|

| 4.3.9 Flash Memory Characteristics              | 25 |

| 4.3.10 IO Input Pin Characteristics             | 26 |

| 4.3.11 IO Output Pin Characteristics            | 26 |

| 4.3.12 NRST Reset Pin Characteristics           | 27 |

| 4.3.13 TIM Counter Characteristics              | 27 |

| 4.3.14 ADC Characteristics                      | 27 |

| 4.3.15 Three-phase Gate Driver Characteristics  | 30 |

| 4.3.16 Operational Amplifier Characteristics    | 30 |

| 4.3.17 N-MOS Electrical Characteristics         | 31 |

| 4.3.18 P-MOS Electrical Characteristics         | 31 |

| 5 Pin Definition                                | 32 |

| 5.1 TSSOP-25 Package                            | 33 |

| 5.2 Pin Definition                              | 34 |

| 5.3 Pin Multiplexing (AF) Function Table        | 35 |

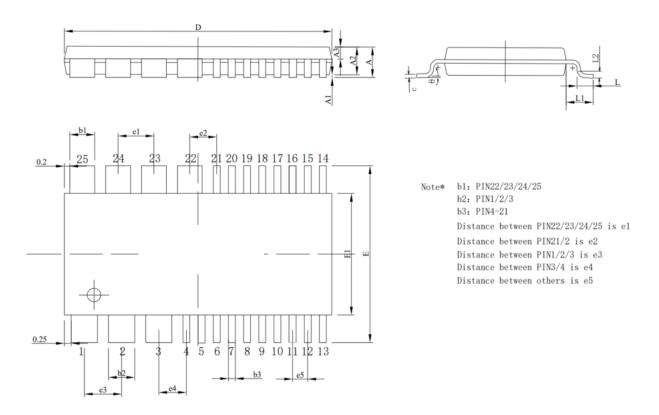

| 6 Package Parameter                             | 37 |

| 6.1 Package Size                                | 37 |

| 6.1.1 TSSOP-25 Package                          | 37 |

| 7 Ordering Information                          | 39 |

| 7.1 Ordering Packaging                          | 39 |

| 8 Acronyms                                      | 40 |

| 9 Revision History                              | 42 |

| 10 Disclaimer                                   | 43 |

## 1 Introduction

The document is the datasheet for the PM30003V-0405 series.

## **2 Product Description**

The PM30003V-0405 MCU utilizes an ARM® Cortex®-M0 core, with a maximum operating freq-uency of 48 MHz. It features built-in 16 KBytes of Flash and 4 KBytes of SRAM. By configuring the Flash controller registers, interrupt vectors can be remapped within the 16 KByte space.

With the exception of power and ground pins, all pins of the PM30003V-0405 MCU can function as GPIO, peripheral IO, or external interrupt inputs. In applications with limited pin count, the MCU provides as many pin signals as possible.

The PM30003V-0405 MCU is equipped with multiple communication interfaces:

- ◆ 2 route high-speed (up to 6 Mbit/s) UART

- ◆ 1 route high-speed (up to 16 Mbit/s) SPI

SPI supports full-duplex or half-duplex communication with data lengths ranging from 4 to 16 bits, master/slave mode, TI mode, NSS pulse mode, and automatic CRC check.

#### ◆ 1 route high-speed (up to 400 Kbit/s) I2C

I2C supports transmission rates of 100/400 kbit/s, master/slave modes, multi-master modes, 7/10-bit addressing, and SMBus protocols. In the MCU halt mode Stop, data reception wake-up is supported.

The PM30003V-0405 MCU features a 16-bit advanced PWM timer (with 4 outputs of PWM, including 3 outputs with dead-time with complementary), a 16-bit general-purpose PWM timer (with 4 outputs of PWM), and a 16-bit basic timer (for timing CPU interrupts).

The PM30003V-0405 MCU has built-in analog circuits: a 12-bit 1 MSPS ADC, an up/down power-on reset circuit POR/PDR/BOR, and an internal reference voltage that is sampled by the ADC on-chip.

The PM30003V-0405 MCU supports a rich set of power consumption modes. In low power consumption mode, this series of MCUs can be automatically woken up by the internal low power consumption timer.

PM30003V-0405 has a built-in three-phase brushless gate driver that can operate at up to 36 V to drive P+N structure MOSFET.

PM30003V-0405 has a built-in 3-way half-bridge P+N type MOS, which supports a lower RDS (ON).

PM30003V-0405 MCU operates within a temperature range of -40°C +105°C and a supply vol tage of 7 V 24 V, which can meet the requirements of most application environments.

Due to its rich peripheral configuration, the PM30003V-0405 MCU is suitable for varies applications.

- Motor drive and speed control

- UAV flight control and gimbal control

- Toy products

- Household appliances

#### Intelligent robot

#### 2.1 Product Features

#### ◆ CPU Core

- ARM® Cortex®-M0

- Maximum clock frequency: 48 MHz

- 24-bit SysTick Timer

- Supports interrupt vector remapping (configured through the Flash controller's registers)

#### Operating Voltage Range

- 7V ~ 24 V

#### **♦** Operating Temperature Range

- -40°C ~ +105°C

### **♦** Typical working current:

- Run working mode: 2.751 mA@48 MHz@5V

Sleep mode: 0.997 mA@48 MHz@5V

- Stop mode: 373.354 μA@5V(LDO normal operation)

- Low-power Stop mode: 6.876μA@5V (LDO low power comsuption)

# ◆ 16 KByte Flash (64 pages, each page 256 Byte; 32-bit data read, 32-bit data write)

- Flash has data security protection function, which can be set to read protection and write protection respectively

- 4 KByte SRAM

#### ◆ CRC hardware unit

#### ◆ Clock

On-chip high-speed clock HSI: 48MHz

On-chip slow clock LSI: 60 kHz

GPIO external input clock: 32MHz

#### ◆ Reset

- Low-level external reset on the NRST pin

- Reset the window watchdog event WWDG

- Independent watchdog event IWDG reset

- Power reset

- Software reset SW reset

- Low power management reset

#### ♦ GPIO port

- Support up to 10 GPIO ports

- Each GPIO can be used as an external interrupt input

- Built-in switchable pull-up and pull-down resistors

- Support open-drain output

- Output drive capability can be configured

#### **♦** Data communication interface

- 2-channel high-speed UART with a maximum speed of 6 Mbit/s

- 1-channel high-speed up to 400 kbit/s I2C: MCU supports data reception wake-up in Stop mode

- 1 channel high-speed SPI up to 18 Mbit/s

#### **♦** Timer and PWM generator

- 1 x 16-bit advanced PWM timer with 4 PWM outputs, 3 complementary outputs with dead zone

- 1 x 16-bit general-purpose PWM timer with 4 PWM outputs

- 1 x 16-bit basic timer supporting CPU interrupt

- 1 x automatic wake-up timer AWUT, which can be used in MCU stop mode

#### ◆ On-chip analog circuit

- 1 x 12-bit 1 MSPS ADC with up to 7 external analog input channels and 2 internal channels, supporting differential pair input

- 1 x 5V/50mA LDO with 5% accuracy

- 2-channel low-offset operational amplifier, supporting millivolt-level signal amplification on current detection resistors

- 1 x upper/lower power reset circuit

- 1 x under-voltage reset circuit

- 1 x internal reference voltage Internal reference voltage is sampled by ADC on chip

#### **♦** Three-phase brushless grid driver

- Three-phase push-pull gate driver for P+N MOS

- Output 10V VGS for low-side NMOS use

- Input voltage VIN undervoltage protection UVLO

- Built-in straight-through prevention function

- Built-in 500nS dead time

- High-end and low-end channel matching

#### ◆ MOSFET

- N-channel:

- VDS =24V, ID =5A

- P-Channel:

- VDS =-24V, ID =-5A

#### CPU tracing and debugging

- SWD debugging interface

- ARM® CoreSightTM Debug Component ROM-Table, DWT, BPU

Customize DBGMCU debug controller low power mode simulation control, debug peripheral clock control, debug and trace interface allocation

#### **♦** ID identification

- Each PM30003V-0405 chip provides a unique 96-bit ID

## 2.2 Device Overview

Table 2-1 PM30003V-0405 Series Feature

|                 | Product Feature                      | PM30003V-0405              |

|-----------------|--------------------------------------|----------------------------|

|                 | GPIO                                 | 10                         |

|                 | Package                              | TSSOP-25                   |

| working voltage |                                      | 7V ~ 24 V                  |

|                 | Working power                        | 50W                        |

|                 | working temperature                  | -40°C~+105°C               |

| Mem             | Flash (Kbyte)                        | 16                         |

| ory             | SRAM (Kbyte)                         | 4                          |

| CDLI            | kernel                               | Cortex®-M0                 |

| CPU             | working frequency                    | 48MHz                      |

|                 | Internal LSI                         | 60KHz                      |

| 时钟              | Internal HSI                         | 48MHz                      |

|                 | External GPIO clock                  | 32MHz                      |

|                 | Advanced timer                       | 1 个(16-bit): TIM1          |

|                 | universal timer                      | 1 个(16-bit): TIM2          |

|                 | Basic timer                          | 1 个(16-bit): TIM6          |

| 定时              | System Tick Timer                    | 1                          |

| 器               | Automatic Wake-up Timer<br>(AWUT)    | 1                          |

|                 | Independent Watchdog (IWDG)          | 1                          |

|                 | Window Watchdog (WWDG)               | 1                          |

| N7 44           | UART                                 | 2                          |

| 通信 接口           | I2C                                  | 1                          |

| JX [-           | SPI                                  | 1                          |

|                 | Number of ADCs and external channels | 1 (7 external channels)    |

| ADC             | Benchmark selection                  | Internal reference voltage |

|                 | ADC sampling rate                    | 1MSPS(12-bit)              |

|                 | ADC accuracy                         | 12-bit                     |

|                 | CRC                                  | 1                          |

|                 | 96-bit UID                           | 1                          |

### **3 Function Introduction**

### 3.1 Block Diagram

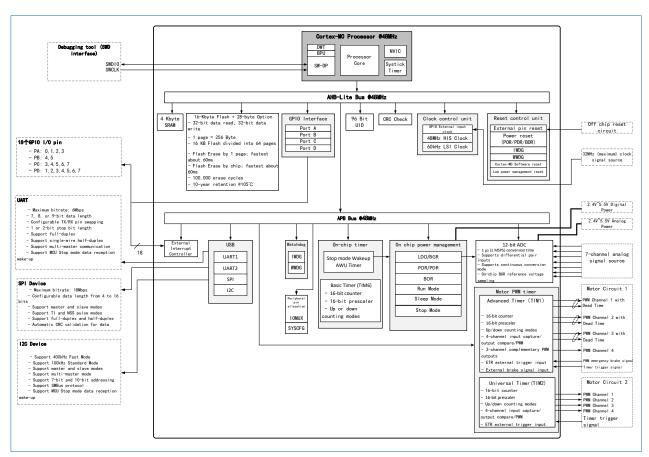

The ARM® Cortex®-M0 processor is an embedded 32-bit RISC processor. It is a low-cost, low-power MCU platform that provides excellent computing performance and advanced interrupt system response. PM30003V-0405 has a built-in Cortex®-M0 core and is compatible with ARM tools and software.

The system architecture of the PM30003V-0405 MCU is illustrated in Figure 1

Figure 3-1 PM30003V-0405 Block Diagram

### 3.2 System Block Diagram

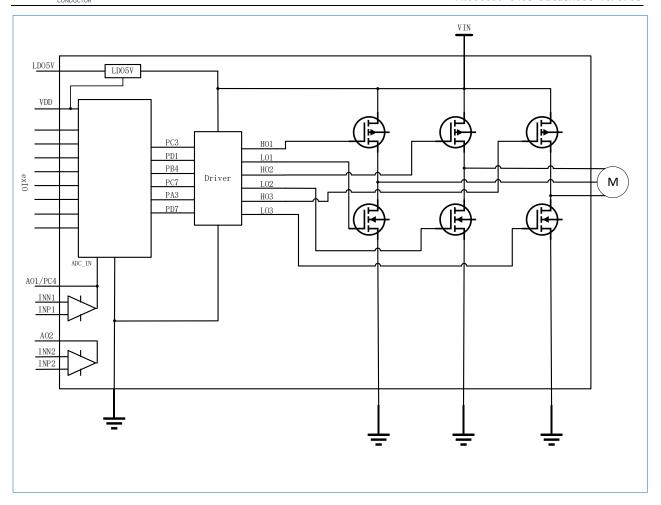

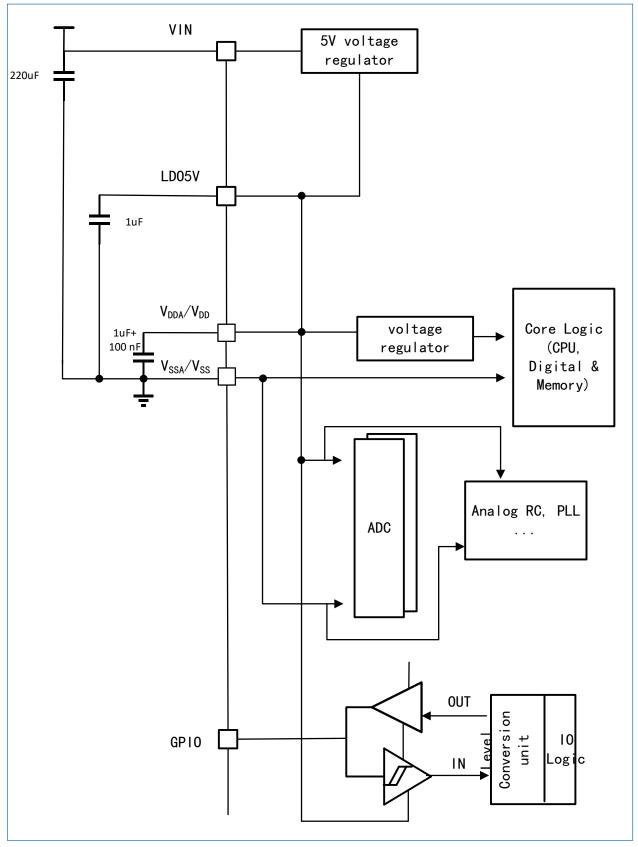

PM30003V-0405 is a highly integrated chip that internally integrates an MCU, Driver, 5V LDO, and three sets of P+N MOS. The system block diagram illustrates the internal resources and connections of PM30003V-0405.

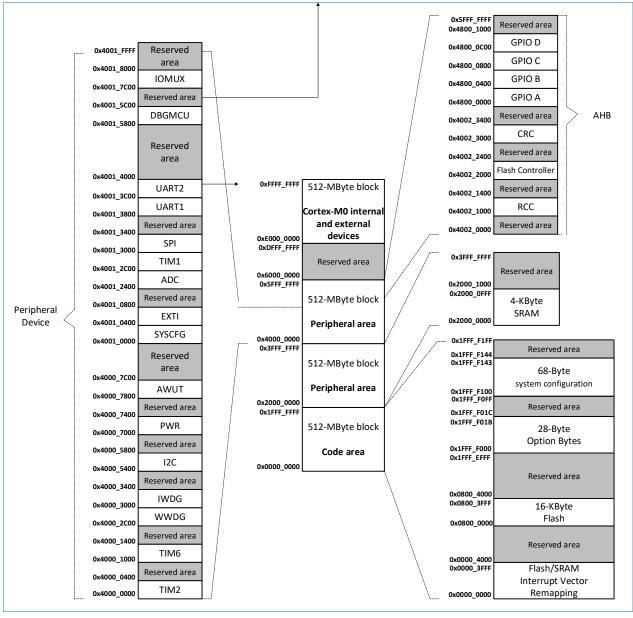

## 3.3 Memory Mapping Configuration

The memory map of the PM30003V-0405 MCU is illustrated in the following figure:

Figure 3-2 PM30003V-0405 Memory Mapping

## 3.4 Memory

#### 3.4.1 Flash

The chip integrates up to 16Kbyte of Flash memory, which is used to store programs and data.

By configuring the registers of the Flash controller, the remapping of interrupt vectors can be achieved.

#### 3.4.2 **SRAM**

The chip integrates 4 Kbyte SRAM inside, supporting word, halfword, and byte read and write access. The CPU can perform fast read and write access with zero wait cycles, which can meet the needs of most applications.

#### 3.5 CRC calculation unit

Cyclic Redundancy Check (CRC) is used to verify the integrity of data transmission or data storage. An independent CRC hardware computing unit is integrated inside the device, which reduces the burden on user applications and provides accelerated processing capabilities.

The CRC calculation unit calculates the signature of the software during operation and compares it with the reference signature generated during linking and stored at a specified storage address.

### 3.6 Power Supply Plan

PM30003V-0405 has two sets of power supplies VIN and LDO5V. VIN provides input 7-24V and outputs 5V to the LDO5V pin, and supplies power to VDD/VDDA.

#### 3.7 Power Monitor

The device integrates a power-on reset POR/power-down reset PDR circuit with an undervoltage reset BOR, which is turned off by default. This circuit is always in operation to ensure that the system works when the power supply exceeds 2.4V. When VDD is lower than the POR/PDR threshold, the device is placed in the reset state without having to use an external reset circuit.

### 3.8 Low power consumption mode

The device supports multiple power consumption modes, achieving an optimal balance between low power consumption, short start-up time, and multiple wake-up events.

Sleep Mode

In sleep mode, only the CPU stops working, and all peripherals are in working state and can wake up the CPU when an interrupt/event occurs.

Stop Mode

The lowest power consumption can be achieved in the halt mode while maintaining the contents of SRAM and registers without loss. In the shutdown mode, all clocks in the kernel domain are turned off, and the RC oscillator of the HSI is turned off. The MCU can be woken up from the halt mode by any signal configured as EXTI. The EXTI signal can be any external I/O port.

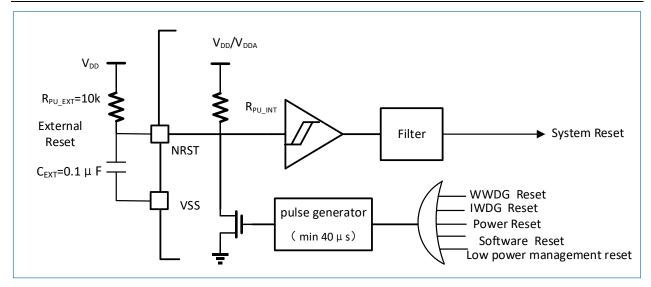

#### 3.9 Reset

The device supports two reset modes: system reset and power reset.

#### 3.9.1 System Reset

In addition to the reset flag bit in the RCC\_CSR register of the clock controller and the registers in the backup area, system reset will reset all registers to their reset state.

Users can identify the source of the reset event by viewing the reset status flag bit in the RCC CSR control status register.

Figure 3-3 Reset Circuit

When any of the following events occurs, a system reset will be generated:

- Low-level external reset on the NRST pin

- Window watchdog count termination WWDG reset

- Independent watchdog count termination IWDG reset

- Power reset

- Software Reset SW Reset: Software reset can be achieved by setting the SYSRESETREQ bit in the Cortex™-M0 interrupt application and reset control register to '1'.

- Low power management reset

The reset source will eventually act on the NRST pin and remain low during the reset process. The reset entry vector is fixed at address 0x0000 0004. The reset signal inside the chip will be output on the NRST pin. The pulse generator ensures that each internal reset source has a minimum pulse delay of  $40\mu s$ . When the NRST pin is pulled low to generate an external reset, it will generate a reset pulse.

#### 3.9.2 Power reset

When any of the following events occurs, a power reset will occur:

- Power-on/power-down reset POR/PDR

- Under-voltage reset BOR

The device integrates a power-on reset POR/power-down reset PDR/under-voltage reset BOR circuit. The POR/PDR circuit is always in working state BOR is turned off by default to ensure the system works normally when the power supply exceeds 2.4 V. When VDD is less than the BOR/POR/PDR threshold, the MCU will be reset without the need for an external reset circuit.

#### 3.10 Clock and clock tree

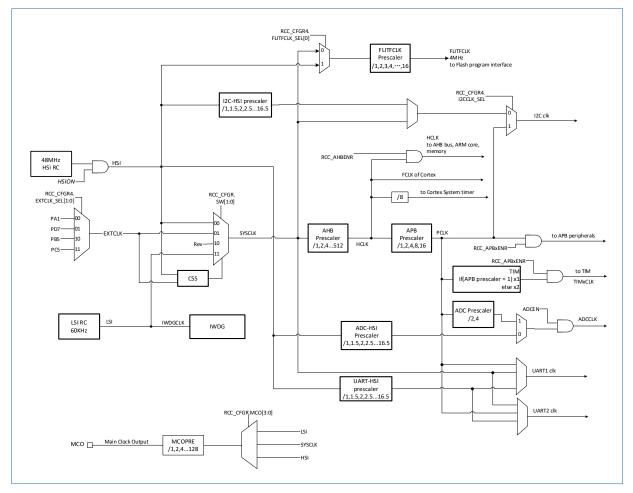

The following is the clock tree of the PM30003V-0405:

Figure 3-4 PM30003V-0405 Clock Tree

As shown in Figure 3 4, PM30003V-0405 supports multiple clock sources to drive system clocks:

- Internal high-speed clock HSI: 48MHz

- Internal low-speed clock LSI: 60kHz

- GPIO external input clock: 32MHz maximum

Each clock source can be turned on or off independently. When they are not in use, they can be turned off to reduce power consumption. There are multiple frequency dividers available for configuring the AHB and APB clock domains, with a maximum clock frequency of 48 MHz for both AHB and APB domains. The Cortex system timer is driven by the AHB clock HCLK, which can be directly driven by the AHB/8 clock frequency through the Cortex SysTick configuration bit.

All peripheral clocks are driven by their respective bus clock HCLK or PCLK, except for the following:

The clock for the flash programming interface, FLITFCLK, is driven by the HSI clock or SYSCLK, and is selected by software.

The I2C clock is selected by software from one of the following clock sources:

- SYSCLK

- HSI 48 MHz is divided by the I2C-HSI frequency divider

- APB Clock (PCLK)

The FCLK of Cortex is directly provided by the AHB clock HCLK.

AHB bus, ARM core, and memory are directly provided by the AHB clock HCLK.

The ADC clock is selected by software from one of the following clocks:

- APB clock PCLK is divided by ADC frequency divider 2/4

- HSI 48 MHz is divided by ADC-HSI frequency divider

The clock for UART1/UART2 is selected by software from one of the following clock sources:

- PCLK

- SYSCLK

- HSI 48 MHz RC oscillator clock through UART-HSI divider clock

The Timer clock is provided by the APB clock PCLK or APB clock PCLK2 multiplied by 2, and is set by software and executed by hardware.

The RCC divides the AHB clock HCLK8 and uses the result as the external clock for the Cortex system timer SysTick. By setting the SysTick control and status registers, you can select the HCLK/8 clock as the SysTick clock.

#### 3.11 SYSCFG

The device has a set of configuration registers, and the main purpose of the system configuration registers is as follows:

- Remapping of the system boot area.

- Manage the connection between external interrupts and GPIO.

- Managing the reliability characteristics of the system.

#### 3.12 GPIO

Each GPIO pin can be configured by software to output push-pull or open drain, input floating input, pull-up input or pull-down input, or other peripheral function ports. Most GPIO pins are shared with digital or analog peripherals. All GPIO pins have high current passing capability. The peripheral function of the I/O pin can be locked as needed to avoid accidental writing to the I/O register.

## 3.13 Interruptions and Events

#### 3.13.1 NVIC

The device has a built-in nested vector interrupt controller NVIC, which can handle up to 22 maskable interrupt channels, excluding 16 interrupt lines for Cortex®-M0 and 4 interrupt priorities. This module provides flexible interrupt management with minimal interrupt latency.

- The tightly coupled NVIC can achieve low-latency interrupt response processing

- Interrupt vector entry address directly enters the kernel

- Close-coupled NVIC interface

- Allow early processing of interrupts

- Handle late higher priority interrupts

- Support for breaking the tail link function

- Automatically save processor state

- Automatically resume when interrupted, without additional instruction overhead

#### 3.13.2 EXTI

The extended interrupt/event controller contains 11 edge detection interrupt lines for generating interrupt/event requests and waking up the system. Each interrupt line can be configured independently to select triggering events on the rising edge, falling edge, or both edges, and can be individually masked. The pending register is used to maintain the status of the interrupt request. EXTI can detect external interrupt line signals with pulse widths less than the internal clock cycle. According to whether the interrupt/event trigger edge can be configured, EXTI can be divided into two categories: configurable EXTI (abbreviated as configurable EXTI) and fixed EXTI (abbreviated as fixed EXTI). There can be up to 9 configurable interrupt lines.

EXTI 0  $\sim$  EXTI 7 are connected to IO, and the remaining EXTI ports are connected to the following events:

- EXTI 8 connects to the AWD event of ADC

- EXTI 10 connected to I2C Wakeup event

- EXTI 11 connected to the Wakeup event of AWU

EXTI8 and EXTI10 are fixed events without RTSR, FTSR, SWIER, and PR registers. They can only collect the rising edge of events in Stop mode to generate ERQ and IRQ signals to wake up the system. The corresponding interrupt control and status bits are stored in the peripheral module that generates the event source.

#### 3.14 ADC

The ADC characteristics of the device are as follows:

- There are only 9 channels in total. Among them, AINO ~ AIN6 are external channels connected to IO; AIN7 is an internal channel that connects to the internal PMU for power supply voltage calibration within the chip. AIN8 is an internal channel that connects to the internal reference voltage.

- Support differential input mode, AINO and AIN1, AIN2 and AIN3, AIN4 and AIN5 form three groups of differential inputs. When the ADC is configured for differential input mode, AIN7 and AIN8 are ADC channels for sampling internal PMU and reference voltage, and AIN6, AIN7, and AIN8 are not available.

- Only supports a sampling resolution of 12-bit ADC.

#### **3.15 Timer**

PM30003V-0405 includes an advanced timer, a general timer, and a basic timer. The timer function is defined as shown in Table below.

Table 3-1 Definition of Timer Function

| Туре              | Timer<br>Name | Counter<br>Resolutio<br>n | Counter<br>Type                                     | Prescaler<br>Factor | DMA<br>Request | Emergenc<br>y Brake<br>Input | Capture/<br>Compare<br>Channel | Complem<br>entary<br>Output |

|-------------------|---------------|---------------------------|-----------------------------------------------------|---------------------|----------------|------------------------------|--------------------------------|-----------------------------|

| Advanced<br>timer | TIM1          | 16-bit                    | Increment,<br>decrement,<br>increment/d<br>ecrement | 1~65536             | None           | Yes                          | 4                              | 3                           |

| General<br>Timer  | TIM2          | 16-bit                    | Increment, Decrement, Increment/D ecrement          | 1~65536             | None           | None                         | 4                              | None                        |

| Basic Timer       | TIM6          | 16-bit                    | Increment<br>and<br>Decrement                       | 1~65536             | None           | None                         | None                           | None                        |

#### 3.15.1 Advanced Timer

The device integrates an advanced timer TIM1.

The advanced timer TIM1 can be used as a three-phase PWM generator with six channels, or as a complete general-purpose timer. Four independent channels can be used for:

- Input capture

- Output comparison

- Generates PWM edge or center alignment patterns

- Single pulse output

- Complementary PWM output with programmable dead zone insertion function.

When the advanced timer is configured as a 16-bit basic timer, it has the same function as the basic timer. When configured as a 16-bit PWM generator, it has full modulation capability from 0 to 100%. Due to the same internal structure and most functions as the general timer, the advanced timer can operate in conjunction with the general timer through the timer link function to provide synchronization or event link functions.

In debug mode, the counter can be frozen.

#### 3.15.2 General Timer

The device integrates a 4-channel general-purpose timer TIM2.

The general-purpose timer can generate PWM outputs or serve as a simple time reference. TIM2 has a 16-bit auto-reload up/down counter and a 16-bit prescaler. In debug mode, this counter can be frozen.

TIM2 can work with advanced control timers through timer linking functions to provide synchronization or event linking capabilities and can handle quadrature incremental encoder signals and digital outputs from 1 to 3 Hall effect sensors.

#### 3.15.3 Basic Timer

The device integrates a basic timer TIM6.

The basic timer has a built-in 16-bit counter and 16-bit prescaler, and supports increment or decrement counting methods. The basic timer is used to generate CPU timing interrupt requests. In debug mode, the counter can be frozen.

#### 3.16 AWUT Timer

The device integrates an automatic wake-up AWUT timer. The AWUT timer is used to count time in the MCU stop mode and generate an interrupt to wake up the MCU. AWUT has a built-in ultra-low power 22-bit timer, and its working clock can be configured as a GPIO input clock or an on-chip slow clock LSI. The AWUT timer uses a countdown method.

## 3.17 Independent Watchdog (IWDG)

The independent watchdog is clocked by an internal independent RC oscillator LSI with a 12-bit down counter and an 8-bit prescaler. Since the RC oscillator is independent of the main clock, it can operate in a shutdown mode. It can be used as a watchdog to reset the device when a problem occurs, or as a free-running timer to provide timeout management for applications. It can be configured in hardware or software through the option byte. In debug mode, this counter can be frozen.

By configuring the IWDG\_WINR register, the IWDG can operate in window mode.

## 3.18 Window Watchdog (WWDG)

The window watchdog has a 7-bit decrement counter inside. The counter can be set to freerunning mode or used as a watchdog to reset the entire system in the event of a system crash. The window watchdog is driven by the main clock and has the function of early warning interruption. In debug mode, this counter can be frozen.

## 3.19 System Tick Timer

The System Tick timer is dedicated to the operating system and can be used as a standard decrement counter. It has the following characteristics.

- 24-bit down counter

- reload function

When the counter reaches 0, a maskable interrupt can be generated.

- Programmable clock source

#### 3.20 I2C Bus

A single I2C bus interface, capable of operating in master and slave modes, supports both standard and fast modes. The I2C interface supports 7-bit or 10-bit addressing, and supports dual slave address addressing when operating in 7-bit slave mode. The I2C interface has a built-in hardware CRC generator/checker and supports SMBus V2.0/PMBus bus.

Table 3-2 I2C Characteristics

| I2C Characteristics        | I2C       |

|----------------------------|-----------|

| Master/Slave Mode          | Supported |

| Multi-host mode            | Supported |

| Standard/fast mode         | Supported |

| 7/10-bit addressing mode   | Supported |

| Broadcast call             | Supported |

| Event management           | Supported |

| Clock extension            | Supported |

| Software reset             | Supported |

| Digital and analog filters | Supported |

| SMBUS2.0                   | Supported |

| PMBUS1.1                   | Supported |

| Independent clock          | Supported |

| Wake up from the Stop mode | Supported |

## 3.21 Universal asynchronous receiver transmitter (UART)

The device has two universal asynchronous receiver transmitters UART1/UART2 built in. They provide hardware management for multiprocessor communication modes and single-wire half-duplex communication modes, with clock domains independent of the CPU clock.

Table 3-3 UART characteristics

| UART Mode/Characteristics             | UART1/2    |

|---------------------------------------|------------|

| Data word length                      | 7/8/9 bits |

| Multi-processor communication         | Supported  |

| Single-wire half-duplex communication | Supported  |

| Dual clock domain                     | Supported  |

## 3.22 Serial Peripheral Interface (SPI)

It has one SPI interface with a communication rate of up to 18 Mbit/s, supporting slave and master modes, full-duplex and half-duplex communication modes. SPI can use a 3-bit prescaler to generate 8 main mode frequencies, and each frame can be configured with 4-bit to 16-bit data. SPI supports CRC, TI mode, etc., and its characteristics are shown in Table below.

Table 3-4 SPI Characteristics

| SPI Characteristics      | SPI       |

|--------------------------|-----------|

| Hardware CRC calculation | Supported |

| RX/TX FIFO               | Supported |

| NSS pulse mode           | Supported |

| SPI Characteristics | SPI       |

|---------------------|-----------|

| TI mode             | Supported |

## 3.23 Operational Amplifier

The chip has two low offset operational amplifiers built in.

#### 3.24 Built-in Driver

The chip has a built-in three-phase brushless gate driver for driving the P+N structure MOSFET. The built-in input voltage VIN has an under-voltage protection UVLO function, which can effectively prevent the power tube from working at too low a voltage. At the same time, built-in pass-through prevention and dead time are used to prevent the driven high and low side MOSFETs from passing through, effectively protecting the power device.

### 3.25 Input and Output Truth Table

The input pins LINx and HINx control the output status of LOx and HOx. The following Table shows the logical relationship between input and output:

| LINx | HINx | LOx | НОх                  | Function                                                  |  |

|------|------|-----|----------------------|-----------------------------------------------------------|--|

| 0    | 0    | GND | $V_{IN}$             | External NMOS and PMOS are turned off simultaneously      |  |

| 0    | 1    | GND | V <sub>IN</sub> -10V | The external NMOS is turned off and the PMOS is turned on |  |

| 1    | 0    | 10V | V <sub>IN</sub>      | External NMOS is on, PMOS is off                          |  |

| 1    | 1    | GND | V <sub>IN</sub>      | External NMOS and PMOS are turned off simultaneously      |  |

Table 3-5 Input and Output Truth Table

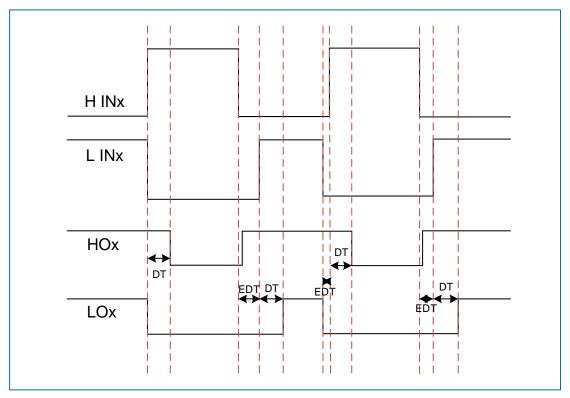

#### 3.25.1 Straight-through Prevention Function

The internal design is specifically designed to prevent the power tube from being directly connected to the protection circuit, effectively preventing damage to the power tube caused by interference with high- and low-side input signals.

Figure 3-5 Straight-through Prevention Function

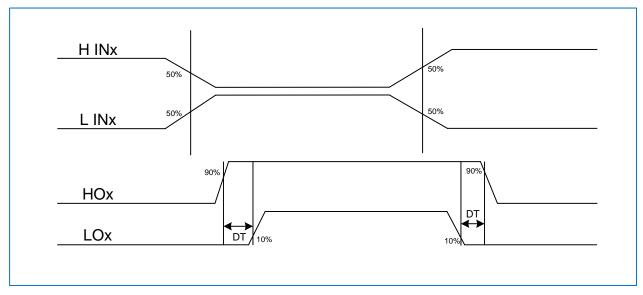

#### 3.25.2 Dead Zone Function

A fixed dead time protection circuit is set up inside. During the dead time, the high side is set to high level and the low side output is set to low level. The dead time must be set to ensure that one power tube is turned off before another power tube is turned on, effectively preventing the occurrence of direct connection between the upper and lower power tubes. If the logic input has an external dead time EDT set, the dead time is equal to the external dead time EDT plus the internally set dead time DT.

Figure 3-6 Dead Time

#### 3.26 LDO

The chip has a built-in 5V/50mA LDO.

#### **3.27 MOSFET**

The chip has 3-way P+N mode RDS(ON) smaller half-bridge MOS.

#### 3.28 96-bit UID

The reference number provided by the 96-bit product unique identity UID is unique to any one of the PM30003V-0405 chips in any situation. The user cannot modify this identity identifier. According to different usages, the 96-bit UID can be read in units of byte 8 bits, half word 16 bits, or full word 32 bits. 96-bit UID is suitable for:

- Used as a serial number, such as a USB character serial number or other terminal applications.

- It is used as a password. When writing flash memory, this UID is used in conjunction with software encryption and decryption algorithms to improve the security of the code within the flash memory.

- Used to activate the bootstrapping process with security mechanisms.

## 3.29 Debugging Interface

The SWJ-DP interface embedded with ARM combines a single-wire debug interface, allowing for the connection of the serial single-wire debug interfaces SWDIO and SWCLK.

## **4 Electrical Characteristics**

## 4.1 Power Supply

Figure 4-1 Power Supply Reference Circuit

## 4.2 Maximum Absolute Ratings

The maximum rated value is only a short-term pressure value.

#### Notes:

- Do not operate the chip at this value or any other conditions exceeding the recommended values.

- Refer to Tables 4.1 to 4.3 for the maximum rated values of the chip. Exceeding the maximum rated values may result in permanent damage to the chip.

- Operating for prolonged periods at maximum rated values may affect the chip's reliability.

#### 4.2.1 Limit Voltage Characteristics

Table 4-1 Limit Voltage Characteristics

| Symbol  | Description                                                      | Minimum | Maximum | Unit |

|---------|------------------------------------------------------------------|---------|---------|------|

| VIN     | Voltage Range                                                    | 6       | 40      |      |

| VINP1,2 | Low Offset Operational Amplifier Positive Input<br>Voltage Rang  | -0.3    | VLDO5V  |      |

| VINN1,2 | Low Offset Operational Amplifier Negative Input<br>Voltage Range | -0.3    | VLDO5V  | V    |

| LCD     | НВМ                                                              | -       | -       |      |

| ESD     | ESD                                                              | -       | -       |      |

#### 4.2.2 Extreme Current Characteristics

Table 4-2 Extreme Current Characteristic

| Voltage Range             | Voltage Range                                                                              | Voltage Range | Voltage<br>Range |

|---------------------------|--------------------------------------------------------------------------------------------|---------------|------------------|

| I <sub>VIN</sub>          | Maximum current flowing through VIN                                                        | 5000          |                  |

| I <sub>VDD</sub>          | Total current passing through $V_{DD}/V_{DDA}$ power lines (supply current) <sup>(1)</sup> | 105           |                  |

| I <sub>vss</sub>          | Total current passing through V <sub>SS</sub> ground lines (drain current) (1)             | 105           |                  |

|                           | Output sinking current on any I/O and control pin                                          | 30            | mA               |

| l <sub>iO</sub>           | Output pulling current on any I/O and control pin                                          | 30            |                  |

| I <sub>INJ(PIN)</sub> (2) | Injection current on I/O pins (3)                                                          | -5/+0         |                  |

| ΣΙ <sub>ΙΝJ(PIN)</sub>    | Total injection current on all I/O and control pins (4)                                    | -25/+0        |                  |

- (1). All power  $(V_{DD}, V_{DDA})$  and ground  $(V_{SS}, V_{SSA})$  pins must always be connected to an external power supply system within the allowable range.

- (2). Reverse injection current can interfere with the analog performance of the device.

- (3). When  $V_{IN} > V_{DD}$ , there is a forward injection current; When  $V_{IN} < V_{SS}$ , there is a reverse injection current. The absolute value of

the injection current must not exceed the specified range.

(4). When several I/O pins have injection currents simultaneously, the maximum value of  $\sum I_{INJ}$  (PIN) is the sum of the instantaneous absolute values of the forward and reverse injection currents.

#### 4.2.3 Limit Temperature Characteristics

Table 4-3 Limit Temperature Characteristic

| Symbol           | Description                  | Minimum | Maximum | Unit |

|------------------|------------------------------|---------|---------|------|

| T <sub>STG</sub> | Storage temperature range    | -55     | 130     | °C   |

| Тյ               | Maximum junction temperature | -45     | 125     | °C   |

## **4.3 Operating Parameters**

### 4.3.1 Recommended Operating Conditions

Table 4-4 Recommended Operating Condition

| Symbol                               | Description                                                      | Minimum | Typical<br>Value | Maximum        | Unit  |  |

|--------------------------------------|------------------------------------------------------------------|---------|------------------|----------------|-------|--|

| Vin                                  | Power supply voltage range                                       | 7       |                  | 24             | V     |  |

| Ivin                                 | V <sub>IN</sub> operating current                                |         | 3000             |                | mA    |  |

| V <sub>LDO5Vout</sub> <sup>(1)</sup> | 5V LDO output voltage range                                      | 4.5     |                  | 5.5            | V     |  |

| ILDO5Vout                            | 5V LDO output current range                                      |         |                  | 50             | mA    |  |

| V <sub>AO1,2</sub> <sup>(2)</sup>    | Low offset op-amp output voltage range                           | 0       |                  | <b>V</b> LDO5V | V     |  |

| V <sub>INP1,2</sub> (2)              | Low offset op-amp positive input voltage range                   | 0       |                  | <b>V</b> LDO5V | V     |  |

| V <sub>INN1,2</sub> (2)              | Negative input voltage range of low offset operational amplifier | 0       |                  | <b>V</b> LDO5V | V     |  |

| f <sub>HCLK</sub>                    | Internal APB Clock Frequency                                     | -       |                  | 48             | NALL- |  |

| f <sub>PCLK1</sub>                   | Internal APB1 Clock Frequency                                    | - 4     |                  | 48             | MHz   |  |

| T <sub>A</sub>                       | Operating Temperature                                            | -40     |                  | 105            | °C    |  |

(1).  $V_{\text{DDA}}$  and  $V_{\text{DD}}$  are Internally Connected.

### 4.3.2 On/Off Reset Characteristics

Table 4-5 On/Off Reset Characteristics

| Symbol                   | Parameter    | Condition    | Minimum | Typical Value | Maximum | Unit |

|--------------------------|--------------|--------------|---------|---------------|---------|------|

| V <sub>POR/PDR</sub> (1) | On/Off reset | Falling edge | 1.68    | 1.80          | 1.93    | V    |

|                          | threshold    | Rising edge  | 1.85    | 1.96          | 2.07    | V    |

| Symbol                    | Parameter      | Condition | Minimum | Typical Value | Maximum | Unit |

|---------------------------|----------------|-----------|---------|---------------|---------|------|

| $V_{PDRhyst}$             | PDR hysteresis | -         | 140     | 160           | 170     | mV   |

| t <sub>RSTTEMPO</sub> (2) | Reset time     | -         | -       | 2             | -       | ms   |

- (1) PDR and POR only monitor  $V_{\text{DD}\,\circ}$

- (2) Design guarantee.

## 4.3.3 Under-voltage Reset Characteristics

Table 4-6 Under-voltage Reset Characteristics

| Symbol                  | Parameter                                                       | Condition (-<br>40~105°C) | Minimum | Typical<br>Value | Maximum | Unit |

|-------------------------|-----------------------------------------------------------------|---------------------------|---------|------------------|---------|------|

|                         |                                                                 | $V_{BOR1}$                | 2.62    | 2.85             | 3.07    |      |

|                         |                                                                 | $V_{BOR2}$                | 3.04    | 3.21             | 3.53    |      |

|                         |                                                                 | $V_{BOR3}$                | 3.45    | 3.64             | 4.01    |      |

|                         | BOR Detection Level Selection (V <sub>DD</sub> Rising Edge)     | $V_{BOR4}$                | 3.89    | 4.04             | 4.46    |      |

|                         |                                                                 | $V_{BOR5}$                | 4.30    | 4.57             | 5.01    |      |

|                         |                                                                 | $V_{BOR6}$                | 4.80    | 5.03             | 5.49    |      |

| $V_{BOR}^{(1)}$         |                                                                 | V <sub>BOR7</sub>         | 5.23    | 5.49             | 5.97    |      |

| V BOR\ <sup>1</sup>     |                                                                 | $V_{BOR1}$                | 2.46    | 2.59             | 2.83    |      |

|                         |                                                                 | $V_{BOR2}$                | 2.84    | 2.99             | 3.26    |      |

|                         |                                                                 | $V_{BOR3}$                | 3.24    | 3.40             | 3.70    |      |

|                         | BOR Detection Level Selection<br>(V <sub>DD</sub> Falling Edge) | $V_{BOR4}$                | 3.68    | 3.80             | 4.14    |      |

|                         |                                                                 | V <sub>BOR5</sub>         | 4.06    | 4.19             | 4.58    |      |

|                         |                                                                 | $V_{BOR6}$                | 4.46    | 4.62             | 5.03    |      |

|                         |                                                                 | V <sub>BOR7</sub>         | 4.84    | 5.05             | 5.48    |      |

| t <sub>BORRST</sub> (2) | Effective Time                                                  | -                         | -       | 10               | -       | μs   |

- (1) BOR only monitors VDD.

- (2) Design guarantee.

## 4.3.4 Internal Reference Voltage

Table 4-7 Internal Reference Voltage Characteristics

| Symbol       | Parameter                        | Condition   | Minimum | Typical Value | Maximum | Unit |

|--------------|----------------------------------|-------------|---------|---------------|---------|------|

| $V_{REFINT}$ | Internal<br>reference<br>voltage | -40 ~ 105°C | -       | 1.2           | -       | V    |

## **4.3.5 Operating Current Characteristics**

Table 4-8 Operating current characteristics

| Made                   | Condition                                                                                                                                                                                                                    | Davamatan.         |         | V <sub>DD</sub> =5V |         | Unit |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|---------------------|---------|------|

| Mode                   | Condition                                                                                                                                                                                                                    | Parameter          | -40°C   | 25°C                | 105°C   | Unit |

| Run Mode               | SYSCLK = HSI48 MHz; All IOs are configured to high impedance state; Except for Flash, SRAM and RCC, all other peripherals are turned off; APB clock enable; To retrieve values from Flash, Flash reads for 2 waiting cycles. | Working<br>current | 2.704   | 2.751               | 2.782   | mA   |

|                        | SYSCLK= 48MHz; AHB/APB is turned off; Turn off the core clock;                                                                                                                                                               | Working<br>current | 1.227   | 1.361               | 1.390   | mA   |

| Sleep Mode             | All IOs are configured to high impedance state; Except for Flash, SRAM and RCC, other peripherals are turned off; RAM and peripheral data are retained.                                                                      | Wake up<br>time    | -       | 2.72                | -       | μs   |

|                        | SYSCLK= 60kHz; All IOs are configured to high impedance state;                                                                                                                                                               | Working<br>current | 0.875   | 0.997               | 1.014   | mA   |

|                        | Except for Flash, SRAM and RCC, all other peripherals are turned off; APB clock is prohibited; Get value from Flash, Flash reads 0 waiting cycles                                                                            | Wake up<br>time    | -       | 1.63                | -       | ms   |

|                        | All Core domain clocks stop; HSI and LSI oscillators are turned off; LDO operates in normal mode;                                                                                                                            | Working<br>current | 343.475 | 373.354             | 453.543 | μА   |

| Stop Mode              | All IOs are configured to high impedance state; All peripherals are turned off except for AWUT;                                                                                                                              | Wake up<br>time    | -       | 32.4                | -       | μѕ   |

|                        | All clocks stop; HSI and LSI oscillators are turned off; LDO operates in low power                                                                                                                                           | Working<br>current | 5.705   | 6.876               | 27.260  | μΑ   |

| Low-Power Stop<br>Mode | consumption mode; All IO configurations are set to high impedance state; All peripherals including AWUT are turned off;                                                                                                      | Wake up<br>time    | -       | 125.5               | -       | μs   |

## 4.3.6 Internal High-speed HSI Clock Characteristics

Table 4-9 HSI Clock Characteristics

| Symbol                          | Parameter          | Condition | Minimum | Typical<br>Value | Maximu<br>m | Unit |

|---------------------------------|--------------------|-----------|---------|------------------|-------------|------|

| f <sub>HSI</sub> <sup>(1)</sup> | Clock<br>frequency | -         | -       | 48               | -           | MHz  |

| DuCy (HSI) (1)                  | Duty cycle         | -         | 45      | -                | 55          | %    |

| Symbol                    | Parameter                             | Condition                                           |                                | Minimum | Typical<br>Value | Maximu<br>m | Unit |

|---------------------------|---------------------------------------|-----------------------------------------------------|--------------------------------|---------|------------------|-------------|------|

| Oscillator Oscillator     |                                       |                                                     | calibrates the RCC_CR register | -1      | ı                | 1           |      |

| ACC (HSI)                 | accuracy                              | Factory<br>calibration                              | T <sub>A</sub> = -40 ~ +105°C  | -1.6    | ı                | 1.6         | %    |

| T <sub>su (HSI)</sub> (1) | Oscillator start time                 | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DD</sub> |                                | -       | 5                | 8           | μs   |

| I <sub>DD (HSI)</sub> (1) | Power<br>consumption<br>of oscillator | -                                                   |                                | -       | 70               | 85          | μА   |

(1) Design guarantee.

## 4.3.7 Internal Low-speed LSI Clock Characteristics

Table 4-10 LSI Clock Characteristics

| Symbol                    | Parameter                       | Condition                      | Minimum | Typical<br>Value | Maximum | Unit |

|---------------------------|---------------------------------|--------------------------------|---------|------------------|---------|------|

| f <sub>LSI</sub>          | Clock frequency                 | -                              | -       | 60               | -       | kHz  |

| T <sub>su</sub> (LSI) (1) | Oscillator start time           | $V_{SS} \le V_{IN} \le V_{DD}$ | -       | 50               | 150     | μs   |

| I <sub>DD (LSI)</sub> (1) | Power consumption of oscillator | -                              | -       | 0.2              | -       | μА   |

(2) Design guarantee.

## 4.3.8 GPIO External clock input characteristics

Table 4-11 GPIO External clock input characteristics

| Symbol                | Parameter                            | Condition | Minimum | Typical<br>Value | Maximum | Unit |

|-----------------------|--------------------------------------|-----------|---------|------------------|---------|------|

| f <sub>GPIO_ext</sub> | User external clock source frequency | -         | 0       | -                | 32      | MHz  |

| DuCy (HSE) (1)        | Duty cycle                           | -         | 45      | -                | 55      | %    |

(3) Design guarantee.

## **4.3.9 Flash Memory Characteristics**

Table 4-12 Flash Memory Characteristics

| Symbol              | Parameter               | Minimum | Typical Value | Maximum | Unit |

|---------------------|-------------------------|---------|---------------|---------|------|

| T <sub>PROG</sub>   | Half-word write time    | -       | 20            | -       | μs   |

| T <sub>ERASE</sub>  | Page erase time         | 30      | 60            | 80      | ms   |

|                     | Chip erase time         | 30      | 60            | 80      | ms   |

| I <sub>DDPROG</sub> | Half-word write current | -       | -             | 5       | mA   |

| Symbol               | Parameter               | Minimum | Typical Value | Maximum | Unit |

|----------------------|-------------------------|---------|---------------|---------|------|

| I <sub>DDERASE</sub> | Page/chip erase current | -       | -             | 2       | mA   |

|                      | Read current @24MH      | -       | 2             | 3       | mA   |

| I <sub>DDREAD</sub>  | Read current @1MHz      | -       | 0.25          | 0.4     | mA   |

| N <sub>END</sub>     | Write/erase endurance   | 100     | -             | -       | 千次   |

| t <sub>RET</sub>     | Data retention time     | 10      | -             | -       | 年    |

## 4.3.10 IO Input Pin Characteristics

Table 4-13 IO Input Pin Characteristics

| Symb<br>ol                     | Parameter                             | Condition                                      | Minimum              | Typical<br>Value | Maximum             | Unit |

|--------------------------------|---------------------------------------|------------------------------------------------|----------------------|------------------|---------------------|------|

| V <sub>IH</sub>                | Input High Level                      | -                                              | 0.65*V <sub>DD</sub> | -                | -                   | V    |

| V <sub>IL</sub>                | Input Low Level                       | -                                              | -                    | -                | 0.2*V <sub>DD</sub> | V    |

| V <sub>IHhys</sub>             | Input High Level                      | V <sub>DD</sub> =5V                            | 2.31                 | -                | -                   | V    |

| V <sub>ILhys</sub>             | Input Low Level                       | V <sub>DD</sub> =5V                            | -                    | -                | 2.23                | V    |

| V <sub>hys</sub>               | Schmitt Trigger<br>Hysteresis Voltage | V <sub>DD</sub> =5V                            | 80                   | -                | -                   | mV   |

|                                | land Lade - Count                     | V <sub>DD</sub> =5V; 0 <v<sub>IN&lt;5V</v<sub> | -                    | 5                | -                   | nA   |

| I <sub>lkg</sub>               | Input Leakage Current                 | V <sub>DD</sub> =3.3V; V <sub>IN</sub> =5V     | -                    | 5                | -                   | nA   |

| R <sub>PU</sub>                | Pull-up Resistor                      | -                                              | -                    | 33               | -                   | ΚΩ   |

| R <sub>PD</sub>                | Pull-down Resistor                    | -                                              | -                    | 33               | -                   | ΚΩ   |

| C <sub>IO</sub> <sup>(1)</sup> | I/O Pin Capacitance                   | -                                              | -                    | -                | 10                  | pF   |

<sup>(4)</sup> Design guarantee.

## 4.3.11 IO Output Pin Characteristics

Table 4-14 IO Output Pin Characteristics

| Symb<br>ol      | Parameter         | Condition                    | Minimum             | Typical<br>Value | Maximum              | Unit |

|-----------------|-------------------|------------------------------|---------------------|------------------|----------------------|------|

| V <sub>OH</sub> | Output High Level | 2.4V ≤ V <sub>DD</sub> ≤5.5V | 0.8*V <sub>DD</sub> |                  |                      | V    |

| V <sub>OL</sub> | Output Low Level  | 2.4V ≤ V <sub>DD</sub> ≤5.5V |                     |                  | 0.2* V <sub>DD</sub> | V    |

Table 4-15 IO Output Driver Pin Characteristics

| Driver geer | V <sub>DD</sub> =3.3V |                 | V <sub>DD</sub> =5V |                 | 3V V <sub>DD</sub> =5V |  | Unit |

|-------------|-----------------------|-----------------|---------------------|-----------------|------------------------|--|------|

| Driver gear | Inject current        | Pull-up current | Inject current      | Pull-up current | Onit                   |  |      |

| Level1      | 4.17                  | 5.24            | 7.86                | 17.83           | mA                     |  |      |

| Duinen      | V <sub>DD</sub> =3.3V |                 | V <sub>DD</sub> | 11-24           |      |

|-------------|-----------------------|-----------------|-----------------|-----------------|------|

| Driver gear | Inject current        | Pull-up current | Inject current  | Pull-up current | Unit |

| Level2      | 16.86                 | 13.64           | 28.29           | 45.89           | mA   |

| Level3      | 23.73                 | 16.78           | 39.82           | 59.93           | mA   |

#### 4.3.12 NRST Reset Pin Characteristics

The NRST pin integrates a pull-up resistor inside, and the peripheral application circuit can be connected to any circuit or an external RC circuit.

Table 4-16 NRST Pin Input Characteristics

| Symbol             | Parameter            | Minimum | Typical Value | Maximum | Unit |

|--------------------|----------------------|---------|---------------|---------|------|

| T <sub>Noise</sub> | Low-level is ignored | -       | -             | 80      | ns   |

#### **4.3.13 TIM Counter Characteristics**

Table 4-17 TIM Pin Input Characteristics (1)

| Symbol           | Parameter                          | Minimum | Maximum                 | Unit |

|------------------|------------------------------------|---------|-------------------------|------|

| F <sub>EXT</sub> | External clock frequency for Timer | -       | f <sub>TIMxCLK</sub> /2 | MHz  |

(1). Design guarantee,  $f_{TIMxCLK} = 48MHz$ .

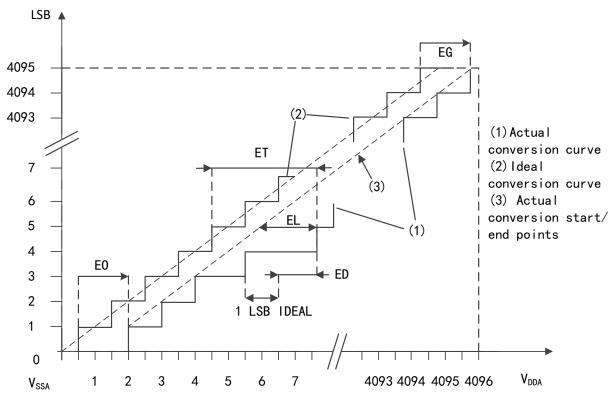

#### 4.3.14 ADC Characteristics

Table 4-18 ADC Characteristics

| Program                       | Description                          | Condition                 | Minimum         | Typical<br>Value | Maximum | Unit   |

|-------------------------------|--------------------------------------|---------------------------|-----------------|------------------|---------|--------|

| $V_{\text{DDA}}$              | Analog supply voltage when ADC is on | -                         | 2.4             | 5                | 5.5     | V      |

| VREFP                         | Positive reference voltage           | -                         | 2.4             | 5                | 5.5     | V      |

| VREFN                         | Negative reference voltage           | -                         | 0               | 0                | 0       | V      |

| f <sub>ADC</sub>              | ADC clock frequency                  | -                         | 0.3             | 12               | 28      | MHz    |

| f <sub>S</sub> <sup>(1)</sup> | sampling frequency                   | f <sub>ADC</sub> = 12 MHz | -               | 1                | -       | MHz    |

| £ (1)                         | External trigger frequency           | f 42 MU-                  | -               | -                | 706     | kHz    |

| f <sub>TRIG</sub> (1)         |                                      | f <sub>ADC</sub> = 12 MHz | 17              | -                | -       | Cycles |

| V <sub>AIN</sub>              | Conversion voltage range             | -                         | VREFN           | -                | VREFP   | V      |

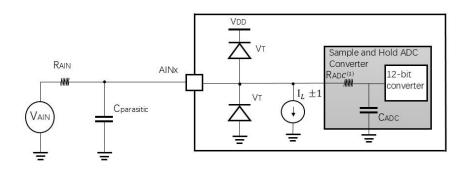

| R <sub>AIN</sub> (1)          | External input impedance             | Please re                 | efer to Table 4 | -19 for details  | s       | kΩ     |

| R <sub>ADC</sub> (1)          | Sampling switch resistance           | -                         | -               | -                | 2       | kΩ     |

| C <sub>ADC</sub> (1)          | sample-and-hold capacitor            | -                         | -               | 5                | -       | pF     |

| Jitterado                     | ADC trigger conversion jitter        | -                         | -               | 1                | -       | Cycles |

| Program               | Description                                          | Condition                                     | Minimum | Typical<br>Value | Maximum | Unit   |

|-----------------------|------------------------------------------------------|-----------------------------------------------|---------|------------------|---------|--------|

| t <sub>S</sub> (1)    | Sampling time                                        | f <sub>ADC</sub> = 12 MHz                     | 1.5     | -                | 239     | Cycles |

| t <sub>CONV</sub> (1) | The total conversion time includes the sampling time | f <sub>ADC</sub> = 12 MHz<br>12bit resolution | 14      | -                | 252     | Cycles |

- (1) Design guarantee.

- (2) The specified values only include the ADC timing. It does not include the delay of register access. The calculation formula for the maximum input impedance RAIN needs to satisfy:  $\mathbf{R}_{AIN} < \frac{Ts}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$

$$R_{AIN} < \frac{Ts}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

Among them, the value of N resolution is 12.

The allowable error is less than 1/4 LSB Least Significant Bit, LSB.

Table 4-19 Maximum Input Impedance (fADC = 12 MHz)

| Sampling Period Ts (Cycles) | Sampling Time t <sub>S</sub> (μs) | Maximum Input Impedance (kΩ) |  |  |  |  |

|-----------------------------|-----------------------------------|------------------------------|--|--|--|--|

| 1.5                         | 0.13                              | 0.58                         |  |  |  |  |

| 7.5                         | 0.63                              | 10.88                        |  |  |  |  |

| 13.5                        | 1.13                              | 21.19                        |  |  |  |  |

| 28.5                        | 2.38                              | 46.95                        |  |  |  |  |

| 41.5                        | 3.46                              | 69.28                        |  |  |  |  |

| 55.5                        | 4.63                              | 93.32                        |  |  |  |  |

| 71.5                        | 5.96                              | 120.80                       |  |  |  |  |

| 239.5                       | 19.96                             | 409.34                       |  |  |  |  |

Table 4-20 ADC Accuracy

| Symbol | Parameter                     | Test Conditions                                     | Typical<br>Value | Maximum | Unit |

|--------|-------------------------------|-----------------------------------------------------|------------------|---------|------|

| ET     | Total unadjustable error (1)  |                                                     | -                | 3       |      |

| EO     | Offset error (2)              |                                                     | -                | 1       |      |

| EG     | Gain error <sup>(3)</sup>     | $V_{DD}=V_{DDA}=5V$ ,<br>$f_{ADC}=12 \text{ MHz}$ , | -                | 1       | LSB  |

| ED     | Differential linear error (4) | 1ADC - 12 WITE,                                     | -                | 4       |      |

| EL     | Integral linear error (5)     |                                                     | -                | 2       |      |

- (1). Total non-adjustable error: the maximum deviation between the actual transfer curve and the ideal transfer curve.

- (2). Offset error: The deviation between the first actual conversion and the first ideal conversion.

- (3). Gain error: The deviation between the last ideal transition and the last actual transition.

- (4). Differential linear error: the maximum deviation between the actual step and the ideal step.

- (5). Integral linear error: The maximum deviation between any actual transition and the end point correlation line.

#### Explain:

- ADC accuracy and negative injection current: Avoid injecting negative current on any standard non-robust analog input pin, as this can significantly reduce the accuracy of performing conversions on another analog input pin. It is recommended to add a Schottky diode pin to the standard analog pin that may inject negative current to ground.

- Better ADC performance can be achieved within a limited range of V<sub>DDA</sub>, frequency, and temperature.

- The data is based on characterization results and has not been tested in production.

Figure 4-1 ADC Accuracy Characteristics

#### Explain:

For the parameter descriptions shown in Table 4 20, please refer to Table 4-20.

Figure 4-2 Typical Connection Diagram of ADC

(1). The ADC characteristics of RADC and CADC values are shown in Table 4 24.

C<sub>parasitic</sub> equals PCB capacitance depending on soldering and PCB layout quality plus pad capacitance of approximately 7 pF. A too high tangential value will reduce the conversion accuracy. To compensate for this, f<sub>ADC</sub> should be minimized.

Recommendations for PCB design for ADC sampling: power decoupling should be carried out according to Figure 5-1. To ensure the accuracy of ADC conversion, it is recommended to use ceramic capacitors with a capacitance of 10 nF and place them as close to the chip as possible.

#### 4.3.15 Three-phase Gate Driver Characteristics

Table 4-21 Three-phase Gate Driver Characteristics

| Parameter       | Definition                                              | Minimum | Typical Value | Maximum | Unit |

|-----------------|---------------------------------------------------------|---------|---------------|---------|------|

| t <sub>рт</sub> | Dead time                                               | 300     | 500           | 800     | nS   |

| Тотр            | Overheat protection threshold, turn off the entire chip |         | 160           |         | °C   |

| Тотрнуѕ         | Overheat protection hysteresis                          |         | 20            |         | °C   |

### 4.3.16 Operational Amplifier Characteristics

Table 4-22 Operational Amplifier Characteristics

| Parameter           | Definition                              | Minimum | Typical Value | Maximum              | Unit |

|---------------------|-----------------------------------------|---------|---------------|----------------------|------|

| VOP                 | Operational amplifier operating voltage |         | 5             |                      | V    |

| V <sub>OFFSET</sub> | Offset voltage                          |         | 3             | 7                    | mV   |

| VC <sub>RANGE</sub> | Input common-mode voltage range         | 0       |               | V <sub>OP</sub> -0.2 | V    |

| I <sub>IN</sub>     | Input bias current                      |         |               | 1                    | uA   |

| Parameter           | Definition                 | Minimum | Typical Value | Maximum  | Unit |

|---------------------|----------------------------|---------|---------------|----------|------|

| I <sub>SOURCE</sub> | CE Output sourcing current |         |               |          | uA   |

| I <sub>SINK</sub>   | Output sinking current     | 1000    |               |          | uA   |

| V <sub>SW</sub>     | Output voltage swing       | 0       |               | $V_{OP}$ | V    |

| Classiants          | Rising edge                |         | 8.5           |          | V/us |

| Slew rate           | Falling edge               |         | 5             |          | V/us |

| Av                  | Open-loop achievement      |         | 10            |          | Kv/V |

| BW                  | Bandwidth                  |         | 6             |          | MHZ  |

#### 4.3.17 N-MOS Electrical Characteristics

Table 4-23 N-MOS Electrical Characteristics

| Symbol  | Description                            | Condition               | Minimu<br>m | Typical<br>Value | Maxim<br>um | Unit |  |  |

|---------|----------------------------------------|-------------------------|-------------|------------------|-------------|------|--|--|

|         |                                        | Cut-off characteristics |             |                  |             |      |  |  |

| BVDSS   | Drain-source breakdown voltage         | VGS =0V, ID =250μA      | 40          | ı                | -           | ٧    |  |  |

| IDSS    | Leakage current with gate-source short | VDS =40V, VGS =0V       | -           | -                | 1           | μΑ   |  |  |

| IGSS    | Gate current with drain-source short   | VDS =0V, VGS=±20V       | -           | -                | ±100        | nA   |  |  |

|         | Conduction characteristics             |                         |             |                  |             |      |  |  |

| VGS(th) | Gate-source threshold voltage          | VDS =VGS, ID=250μA      | 1.1         | 1.5              | 2.0         | ٧    |  |  |

| RDS(ON) | Drain-source on-state resistance       | VGS=7V,ID=0.5A          | -           | 15               | -           | mΩ   |  |  |

## 4.3.18 P-MOS Electrical Characteristics

Table 4-24 N-MOS Electrical Characteristics

| Symbol  | Description                                   | Condition           | Minimu<br>m | Typical<br>Value | Maxim<br>um | Unit |  |  |  |

|---------|-----------------------------------------------|---------------------|-------------|------------------|-------------|------|--|--|--|

|         | Cut-off characteristics                       |                     |             |                  |             |      |  |  |  |

| BVDSS   | drain-source breakdown voltage                | VGS =0V, ID =-250μA | -40         | -                | -           | V    |  |  |  |

| IDSS    | drain current in gate-source<br>short circuit | VDS =-40V, VGS =0V  | -           | -                | -1          | μА   |  |  |  |

| IGSS    | Gate current with drain-source short circuit  | VDS =0V, VGS=±20V   | -           | -                | ±100        | nA   |  |  |  |

|         | Conduction characteristics                    |                     |             |                  |             |      |  |  |  |

| VGS(th) | gate-source threshold voltage                 | VDS =VGS, ID=-250μA | -1.0        | -1.5             | -2.0        | V    |  |  |  |

| RDS(ON) | drain-source on-state resistance              | VGS=7V,ID=-0.5A     | -           | 36               | -           | mΩ   |  |  |  |

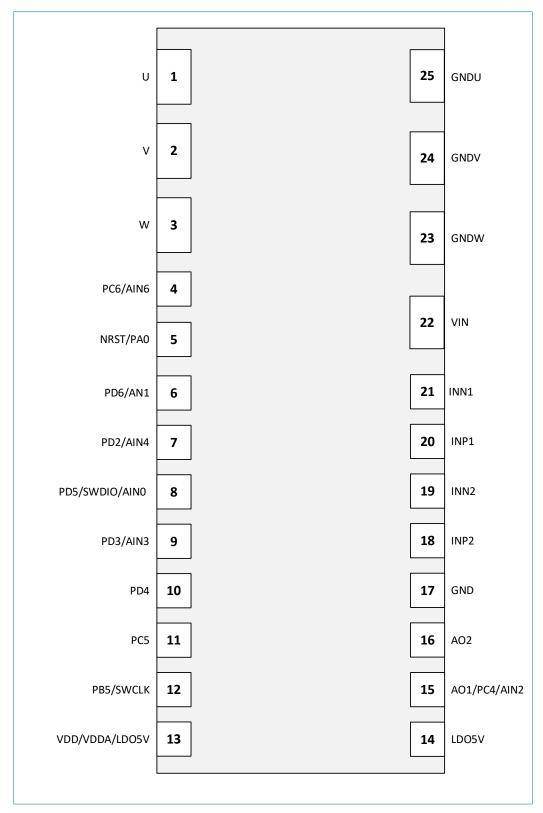

## **5 Pin Definition**

PM30003V-0405 MCU uses TSSOP-25 package, with the following pin definitions.

## 5.1 TSSOP-25 Package

Figure 5-1 TSSOP-25 Package

## **5.2 Pin Definition**

Table 5-1 TSSOP-25 Package Pin Definition

| Pin<br>Number | Pin Name                    | Pin Type <sup>(1)</sup> | Support<br>Tolerant | Default Pin Function<br>after Power-On                                                                              | Default Multiplexed<br>Pin Function (AF0)        |  |

|---------------|-----------------------------|-------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|

| 1             | U                           | 0                       |                     | Phase U Output                                                                                                      |                                                  |  |

| 2             | V                           | 0                       |                     | Phase V                                                                                                             | Output                                           |  |

| 3             | w                           | 0                       |                     | Phase W                                                                                                             | / Output                                         |  |

| 4             | PC6/AIN6                    | 1/0                     |                     | PC6                                                                                                                 | -                                                |  |

| 5             | NRST/PA0                    | I/O                     |                     | NRST                                                                                                                | -                                                |  |

| 6             | PD6/AIN1                    | I/O                     |                     | PD6                                                                                                                 | -                                                |  |

| 7             | PD2/AIN4 <sup>(2)</sup>     | I/O                     |                     | PD2                                                                                                                 | -                                                |  |

| 8             | PD5/SWDIO/AINO (2)          | I/O                     |                     | SWDIO                                                                                                               | SWDIO                                            |  |

| 9             | PD3/AIN3 (2)                | I/O                     |                     | PD3                                                                                                                 | -                                                |  |

| 10            | PD4                         | I/O                     |                     | PD4                                                                                                                 | I2C_SMBA                                         |  |

| 11            | PC5/EXTCLK4                 | I/O                     |                     | PC4/ PC5                                                                                                            | I2C_SDA                                          |  |

| 12            | PB5/SWCLK/EXTCLK3           | I/O                     |                     | SWCLK                                                                                                               | SWCLK_I2C_SDA <sup>(3)</sup>                     |  |

| 13            | VDD/VDDA/LDO5V              | S                       |                     | The digital power supply on the chip is connected to the analog power supply, and internally connected to the LDO5V |                                                  |  |

| 14            | LDO5V                       | 0                       |                     |                                                                                                                     | external 1uF capacitor to und                    |  |

| 15            | AO1/PC4/AIN2 <sup>(2)</sup> | 1/0                     |                     |                                                                                                                     | low-offset operational<br>the input of channel 2 |  |